研究內(nèi)容:

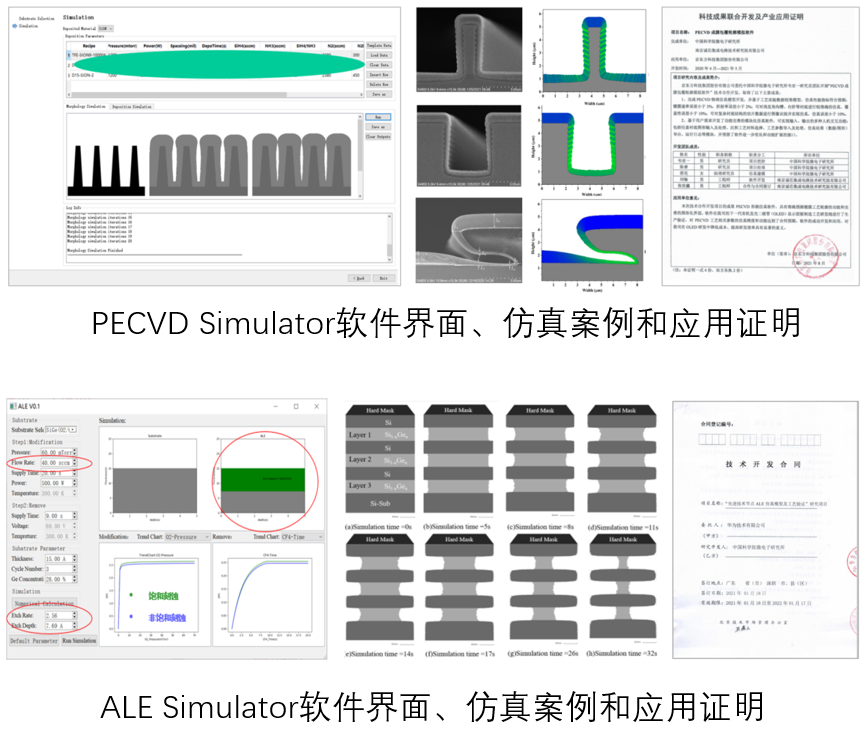

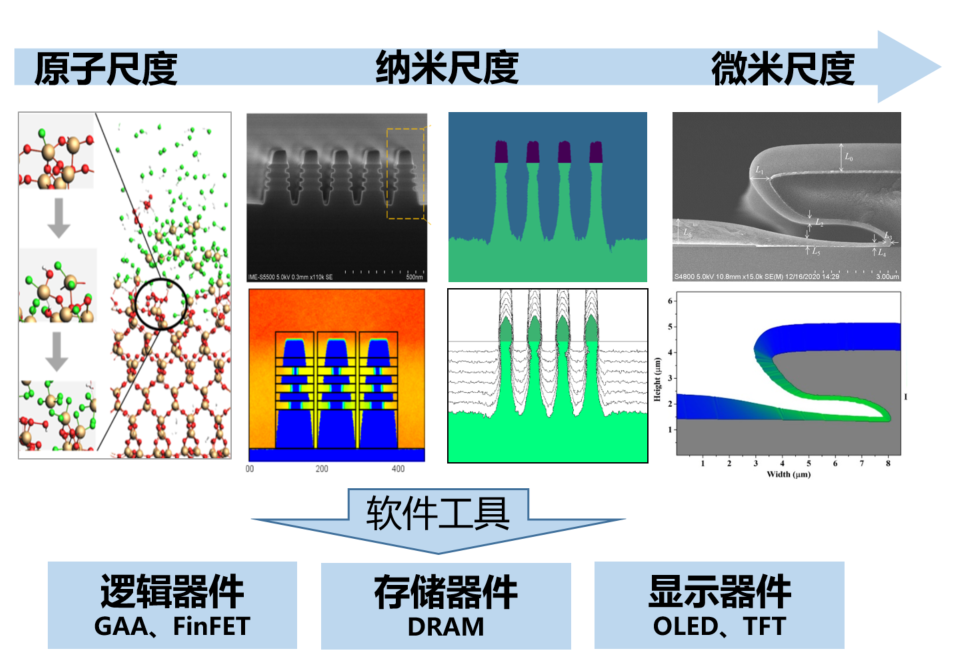

★ 研究面向先進技術(shù)節(jié)點的刻蝕、沉積等工藝的物理模型,反映設(shè)備工藝參數(shù)、襯底幾何形貌等對器件結(jié)構(gòu)微觀尺寸的影響;研究原子尺度工藝仿真的分子動力學(xué)方法;

★ 研究人工智能驅(qū)動的工藝仿真模型,實現(xiàn)器件結(jié)構(gòu)的快速預(yù)測和工藝參數(shù)的快速優(yōu)化;研究基于機器學(xué)習(xí)的刻蝕鄰近效應(yīng)修正模型,提升計算光刻版圖優(yōu)化效果;

★ 開發(fā)滿足業(yè)界需求的全流程工藝仿真工具,面向邏輯器件(FinFET/GAA)、存儲器件(DRAM)、顯示器件(OLED/TFT)等領(lǐng)域的頭部企業(yè)進行技術(shù)轉(zhuǎn)移。

研究成果:

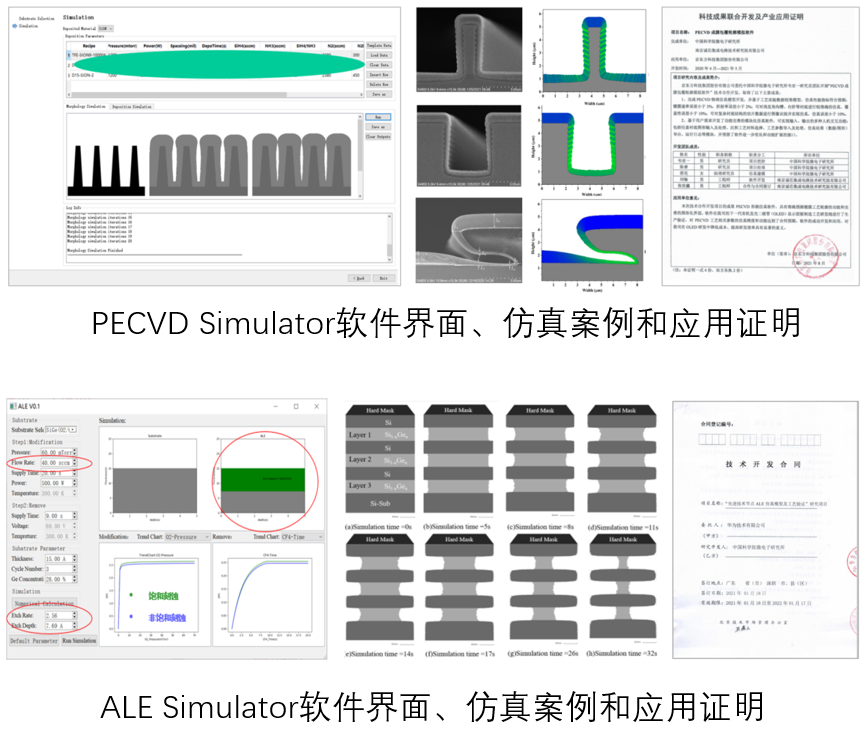

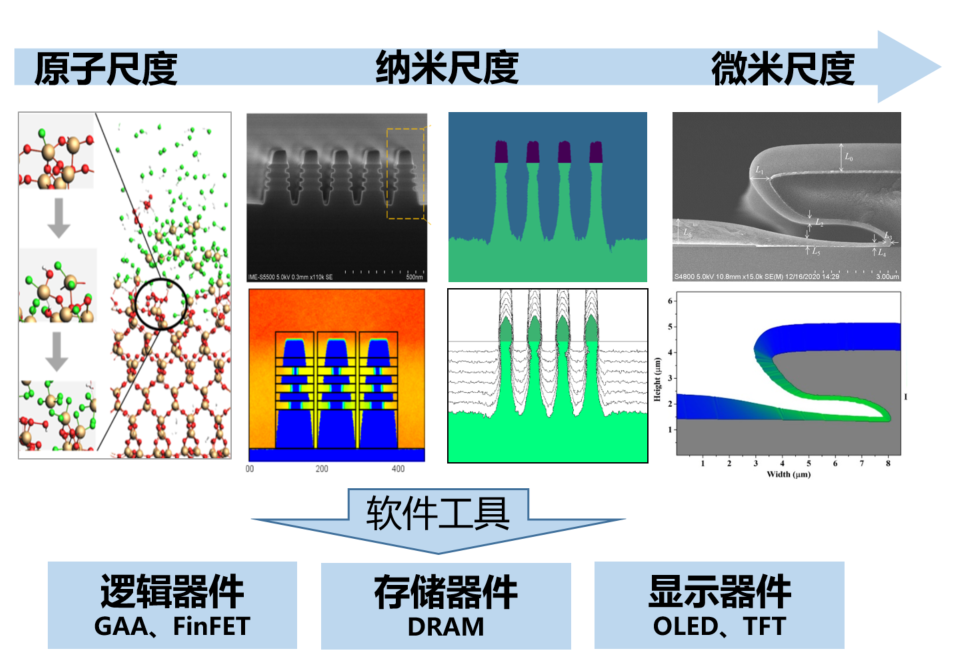

開發(fā)了面向頭部企業(yè)應(yīng)用的刻蝕、沉積工藝物理模型仿真工具:PECVD工藝仿真軟件具備任意襯底結(jié)構(gòu)的薄膜沉積形貌仿真功能,在京東方OLED G6代線完成驗證和應(yīng)用,仿真精度達(dá)到產(chǎn)線要求;ALE先進刻蝕工藝仿真軟件具備環(huán)柵(GAA)晶體管Si/SiGe疊層結(jié)構(gòu)橫向刻蝕仿真功能,與華為合作完成驗證。