研究內(nèi)容:

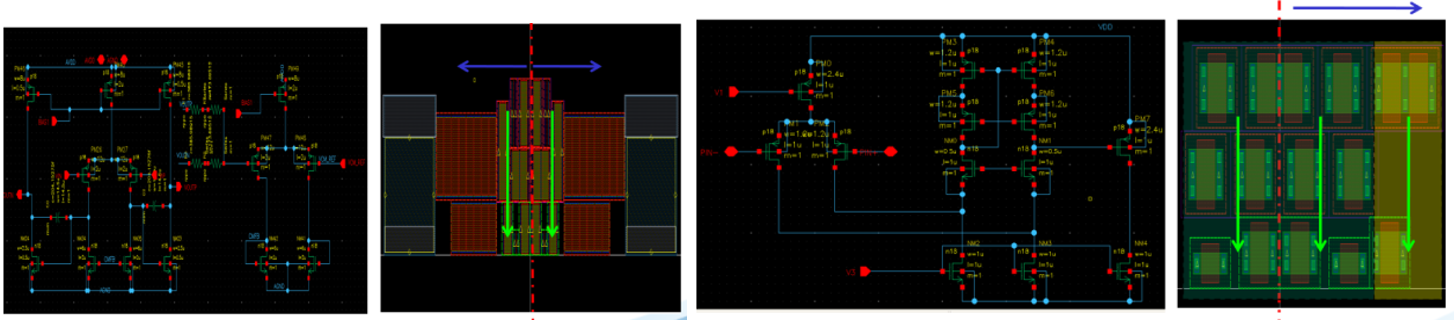

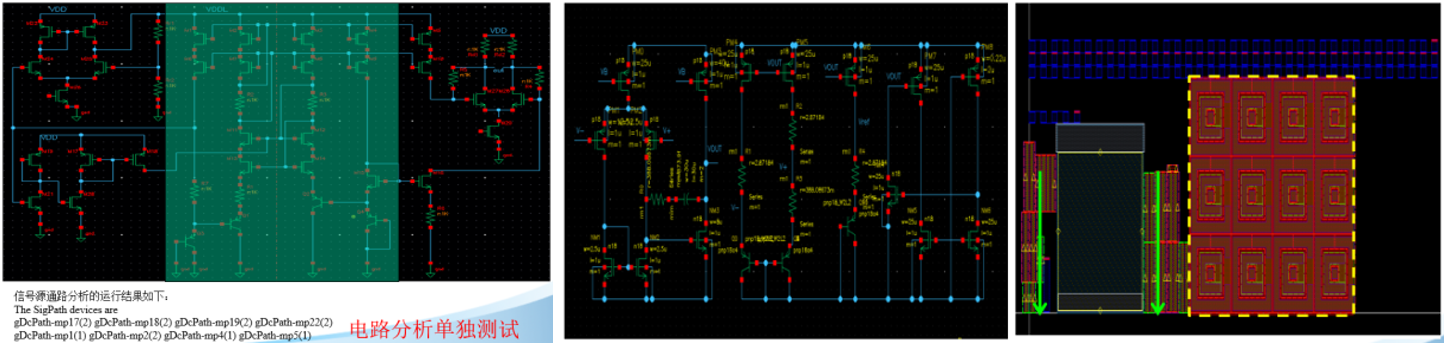

提出了以設(shè)計(jì)完整性貫通整個(gè)模擬集成電路設(shè)計(jì)流程的新思想,實(shí)現(xiàn)了相關(guān)的設(shè)計(jì)自動化工具套件,支持模擬電路設(shè)計(jì)自動化,用于自動提取電路原理圖綜合、器件尺寸設(shè)計(jì)、模塊版圖、電路布局、布線等所需約束條件,并以約束驅(qū)動模擬電路圖自動綜合、電路器件尺寸自動優(yōu)化、模塊版圖自動生成、電路自動布局、自動布線、模擬電路版圖專有的設(shè)計(jì)規(guī)則檢查等,部分成果應(yīng)用于國內(nèi)EDA頭部企業(yè)的軟件工具。獲國家科技重大專項(xiàng)支持。

研究成果:

模擬集成電路設(shè)計(jì)自動化軟件平臺可以自動提取模擬集成電路設(shè)計(jì)電路原理圖綜合、器件尺寸設(shè)計(jì)、模塊版圖、電路布局、布線等所需約束條件,約束驅(qū)動模擬電路圖自動綜合、電路器件尺寸自動優(yōu)化、模塊版圖自動生成、電路自動布局、自動布線,效果接近專業(yè)人員的設(shè)計(jì),并在通用的設(shè)計(jì)規(guī)則檢查之外增加了模擬電路版圖專有的設(shè)計(jì)規(guī)則自動檢查,顯著加速模擬電路設(shè)計(jì)收斂性,提高設(shè)計(jì)效率。