研究內(nèi)容:

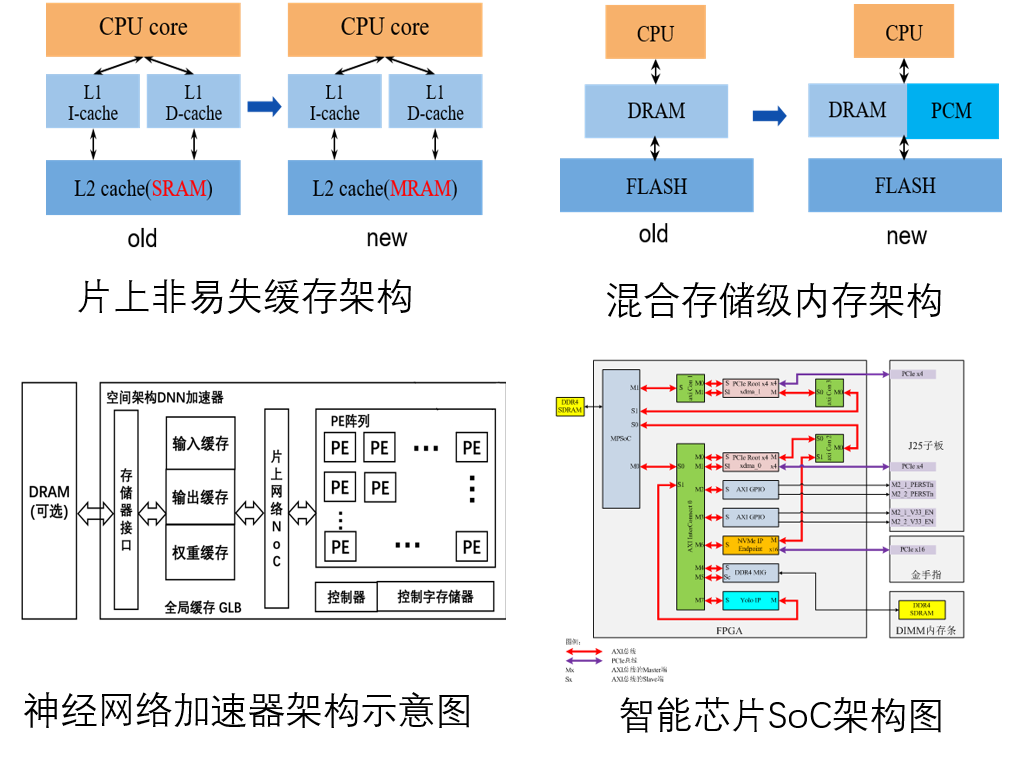

針對AI大數(shù)據(jù)、物聯(lián)網(wǎng)等流式計(jì)算,研發(fā)基于新型非易失存儲(chǔ)器的近存計(jì)算架構(gòu),實(shí)現(xiàn)數(shù)據(jù)存儲(chǔ)和計(jì)算的融合,解決存儲(chǔ)墻問題。研究內(nèi)容主要包括智能芯片近數(shù)據(jù)計(jì)算架構(gòu)技術(shù)、基于STT-RAM等新型非易失存儲(chǔ)器的片上緩存系統(tǒng)、軟硬件協(xié)同優(yōu)化技術(shù)、可重構(gòu)神經(jīng)網(wǎng)絡(luò)加速芯片的設(shè)計(jì)與實(shí)現(xiàn),EDA智能硬件加速應(yīng)用。此項(xiàng)工作得到國家重點(diǎn)研發(fā)計(jì)劃、北京市科技計(jì)劃、中科院先導(dǎo)專項(xiàng)的支持。