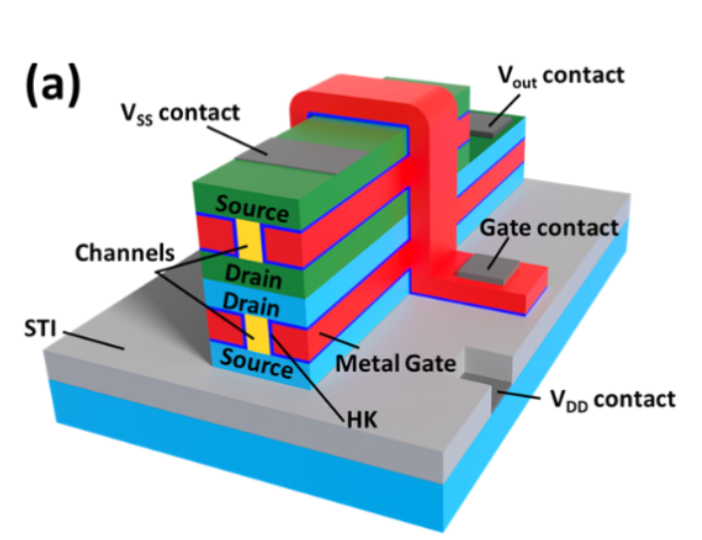

根據(jù)國際器件和系統(tǒng)路線圖(IRDS2023),在集成電路邏輯技術領域,互補場效晶體管(CFET)是繼FinFET和水平GAA之后的下一代晶體管架構。CFET技術通過將NMOS與PMOS器件垂直堆疊,改變傳統(tǒng)平面工藝或FinFET/GAA的水平布局模式,在更小的空間內(nèi)實現(xiàn)更高的集成密度和更佳的性能。近日,微電子所基于自主研發(fā)的垂直溝道技術,提出和研制...

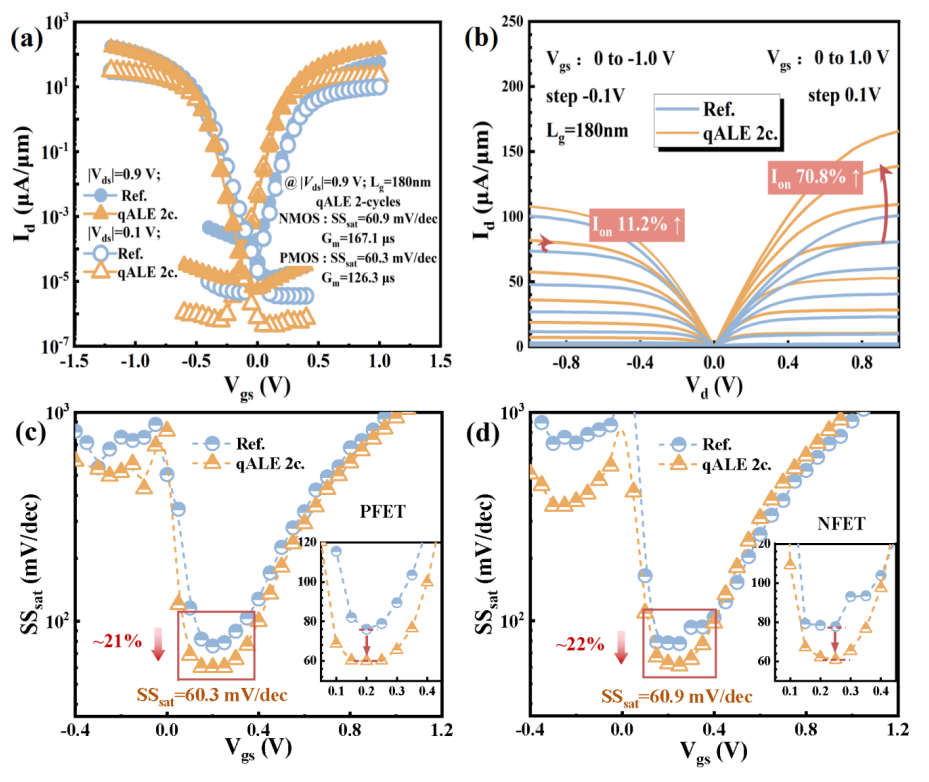

堆疊納米片全環(huán)繞柵(GAA)晶體管具有極佳的柵控特性、更高的驅(qū)動性能以及更多的電路設計靈活性,是主流集成電路制造繼FinFET之后的核心晶體管結構。目前,三星電子(Samsung)、臺積電(TSMC)與英特爾(Intel)等半導體巨頭已經(jīng)或者即將在3納米及以下技術節(jié)點采用該器件進行工藝量產(chǎn)。然而,目前報道的堆疊納米片GAA器件存在溝道...

金屬-氧化物-半導體場效應晶體管(MOSFET)是推動大規(guī)模CMOS集成電路按照“摩爾定律”持續(xù)微縮并不斷發(fā)展的核心器件。近十幾年,為突破更小技術節(jié)點下的微縮挑戰(zhàn),晶體管結構創(chuàng)新成為了技術發(fā)展的主要路徑,從平面晶體管演進到鰭式場效應晶體管,再到最新3nm技術節(jié)點下的堆疊納米溝道全環(huán)繞柵極FET(GAAFET),通過晶體管內(nèi)部溝道...

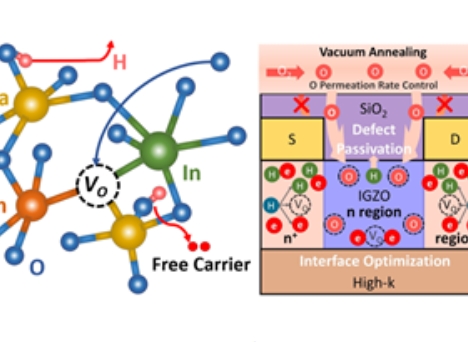

為解決現(xiàn)代計算系統(tǒng)中(如云計算和人工智能)的“內(nèi)存墻”帶寬局限、高效計算瓶頸和制造工藝尺寸微縮等問題,一種結合新型非晶態(tài)氧化銦鎵鋅(IGZO)薄膜材料的無電容(2T0C)DRAM結構,有望取代傳統(tǒng)1T1C DRAM成為關鍵性的新興技術路線。目前,大量研究工作集中于通過器件結構和工藝優(yōu)化來提升IGZO 3D DRAM的保留時間和操...

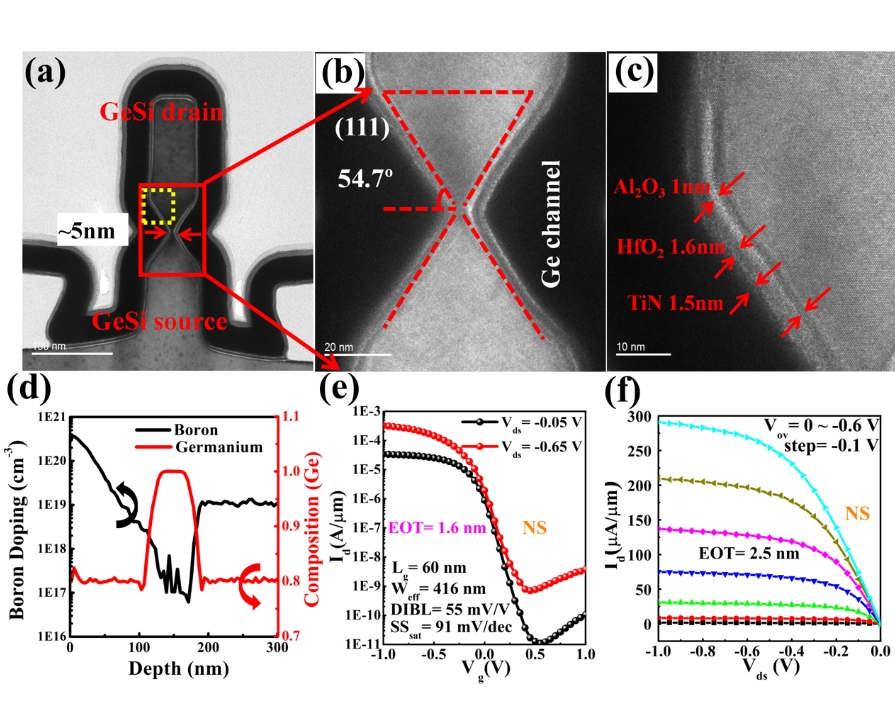

在先進集成電路制造工藝中, 納米環(huán)柵器件(GAA)正取代FinFET成為集成電路中的核心器件。垂直納米環(huán)柵器件由于其在減小標準單元面積、緩解柵極長度限制、提高集成密度和改善寄生電容/電阻等方面具有獨特優(yōu)勢, 成為先進邏輯和DRAM技術方面的重要研究方向。微電子所集成電路先導工藝研發(fā)中心朱慧瓏研究團隊于2016年首次提...

集成電路創(chuàng)新技術