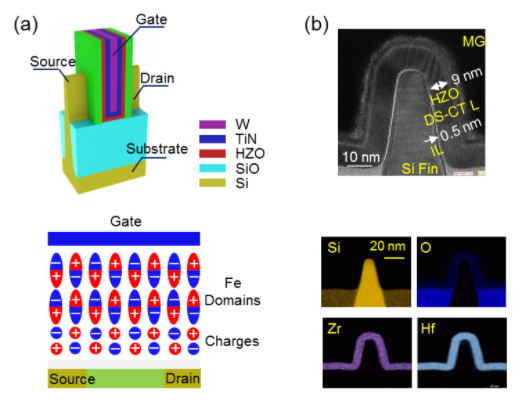

受制于傳統(tǒng)馮諾依曼架構下“存儲墻”問題,芯片的算力難以進一步提升,限制了大數(shù)據(jù)以及人工智能等新興信息技術產(chǎn)業(yè)的發(fā)展。存內(nèi)計算是非馮諾依曼架構下提高芯片算力的一種有效途徑,基于鐵電晶體管( Fe-FET )的存算融合電路由于具有低功耗、高CMOS兼容性以及無損讀出等優(yōu)點,被認為是極具潛力的一種存內(nèi)計算的技術方...

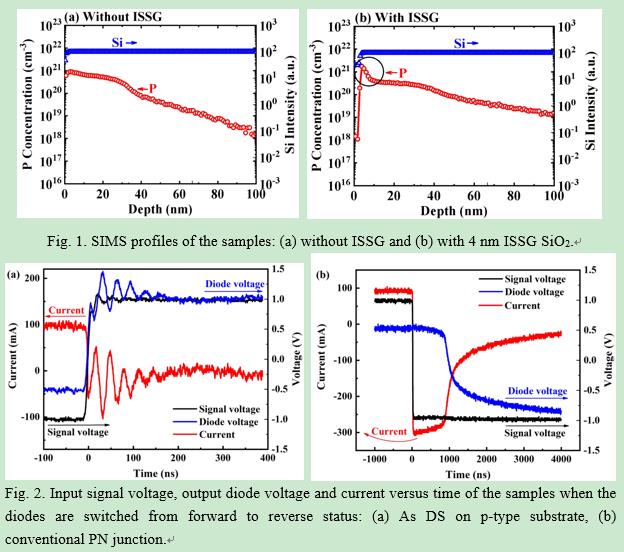

近日,微電子所集成電路先導工藝研發(fā)中心在源漏接觸技術研究方面取得重要進展。隨著集成電路制造技術進入10納米及以下節(jié)點,器件寄生電阻已超過溝道電阻使得器件延遲與功耗顯著增大。阻率可降低源漏寄生電阻,對提升器件性能具有重要意義。提高Si表面雜質激活濃度(Ns)以有效增加接觸界面的載流子隧穿概率,是減小接觸...

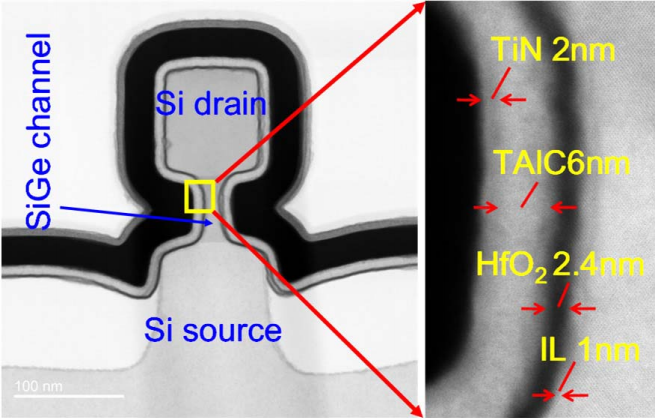

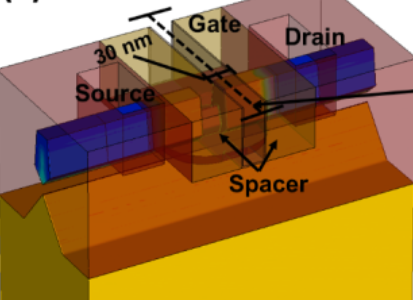

中科院微電子所近期發(fā)表了先導工藝研發(fā)中心團隊在垂直納米環(huán)柵器件領域獲得的最新進展,該類型器件通過在垂直方向構建晶體管結構,大大減少了器件占用面積,在3nm以下先進集成電路制造工藝領域極具應用潛力。針對器件樣品,研究了VSAFET的特性,以及金屬硅化物工藝、 Si-Cap 、溝道Ge含量和熱處理過程等器件性能影響因素...

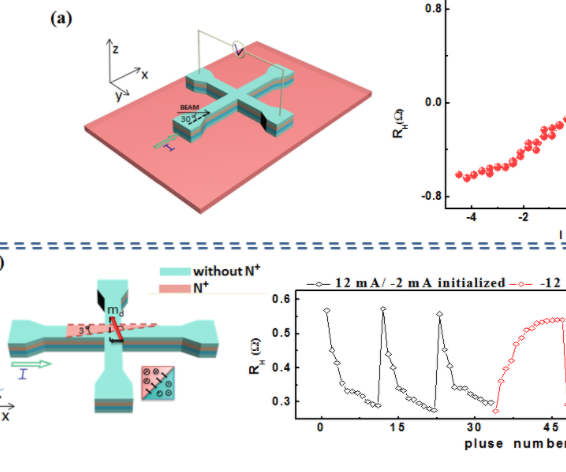

近期,微電子所集成電路先導工藝研發(fā)中心羅軍研究員課題組與中科院半導體所王開友研究員課題組合作研制出全線性的電流誘導多態(tài)自旋軌道耦合( SOT )磁性存儲器件,并實現(xiàn)了低能耗、可編輯的突觸功能,對基于SOT-MRAM的低功耗存算一體邏輯和神經(jīng)形態(tài)計算提供了一種新方法。當前,存算一體和人工智能神經(jīng)網(wǎng)絡芯片領域亟需...

量子計算是未來信息技術發(fā)展的重要方向,在一些特定領域具有較大應用潛力。基于硅量子點的量子比特是實現(xiàn)通用量子計算最有前景的方案之一,具有較長的退相干時間和出色的CMOS制造工藝兼容性。目前,硅量子點量子計算正處在采用集成電路先進制造工藝實現(xiàn)量子點規(guī)模集成并進行量子比特擴展驗證的關鍵研究階段。近期,中國...

集成電路創(chuàng)新技術