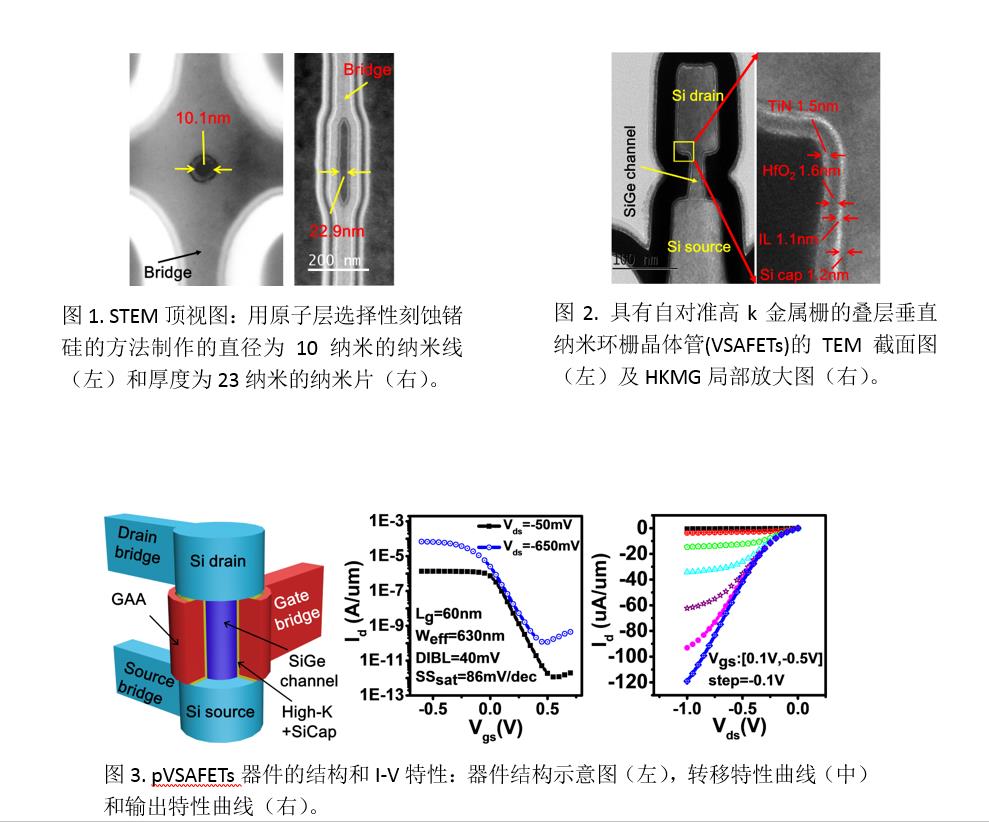

垂直納米環柵晶體管是集成電路2納米及以下技術代的主要候選器件,但其在提高器件性能和可制造性等方面面臨著眾多挑戰。在2018年底舉辦的國際集成電路會議IEDM上,來自IMEC的Ryckaert博士1將垂直納米器件的柵極長度及溝道與柵極相對位置的控制列為關鍵挑戰之一。朱慧瓏課題組系統地研發了一種原子層選擇性刻蝕鍺硅的方法...

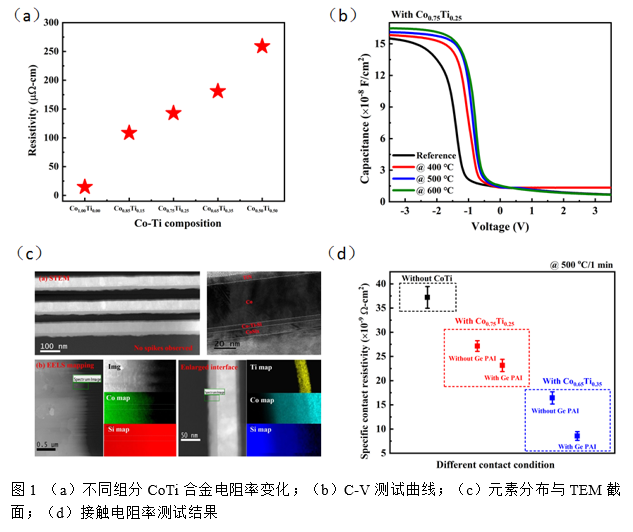

近日,中科院微電子研究所集成電路先導工藝研發中心羅軍研究員課題組在先進Co互連阻擋層研究領域取得了階段性進展。目前, W和Cu被廣泛應用于互連線中,但隨著互連線的線寬不斷減小,電子表面散射與晶界散射會使得互連線電阻率受尺寸效應影響迅速增大。針對先進Co互連,課題組采用Co 、 Ti靶材共濺射方法制備了非晶CoTi...

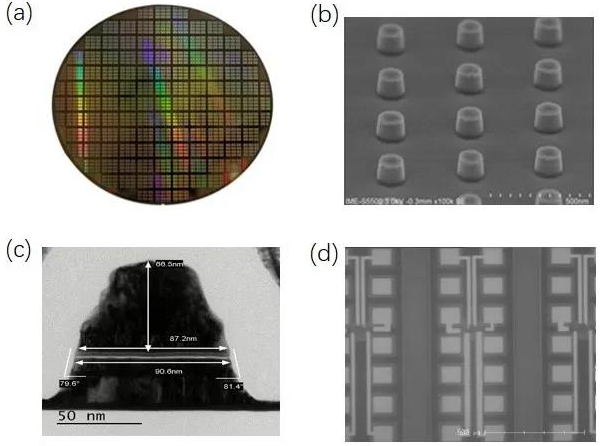

近日,中科院微電子研究所集成電路先導工藝研發中心羅軍研究員課題組在STT-MRAM器件與集成技術研究領域取得了階段性進展。課題組聯合北航趙巍勝教授團隊以及江蘇魯汶儀器有限公司,基于8 吋 CMOS先導工藝研發線,自主研發原子層級磁性薄膜沉積、深紫外曝光、原子層級隧道結刻蝕以及金屬互連等關鍵工藝模塊,在國內首次實...

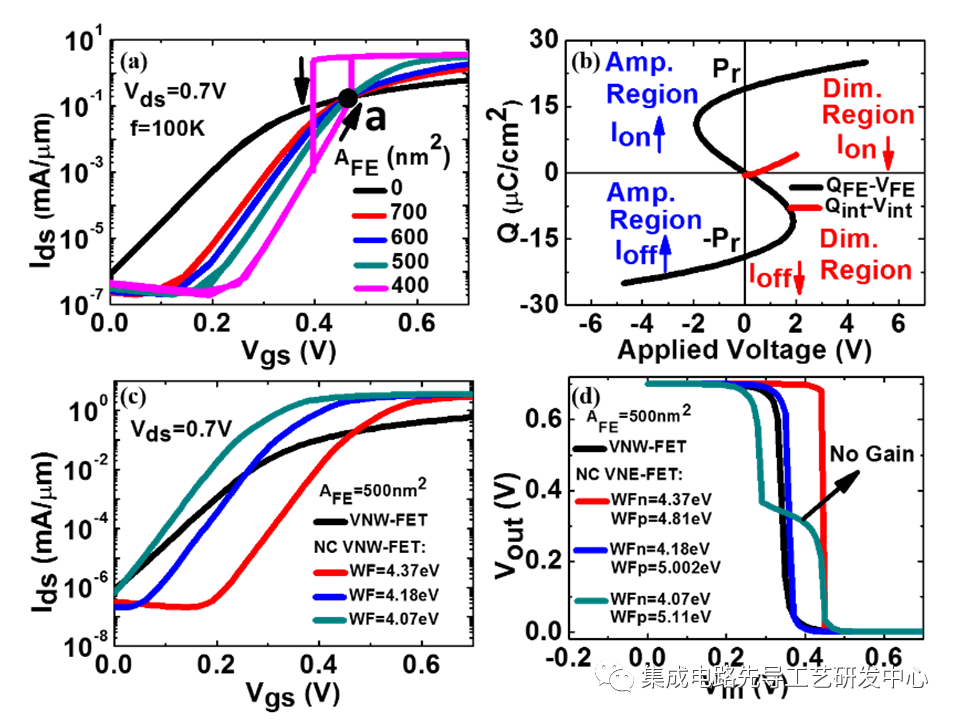

摩爾定律推動了持續50年的集成電路的發展,然而,時至今日,由于物理極限的限制,晶體管的進一步微縮已經舉步維艱。為了進一步增加集成電路性價比,一些基于新原理、新材料、新工藝的晶體管不斷被提出,其中負電容場效應晶體管是近年來被廣泛研究的對象之一。負電容晶體管可以克服“玻爾茲曼熱限制” ,即在室溫下突破亞...

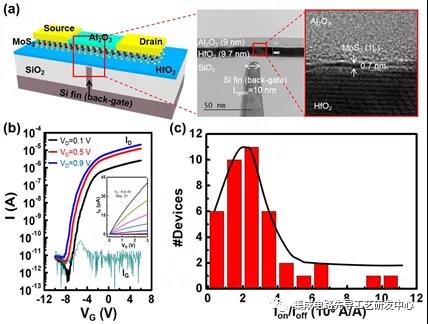

近期,中國科學院微電子研究所集成電路先導工藝研發中心在新型二維材料器件面向未來集成電路集成應用研發中取得重要進展,結合硅基FinFET工藝成功研制出10nm超短物理柵長二硫化鉬晶體管,實現電流開關比達到107 。二維半導體材料具有原子級的厚度,被用作晶體管的溝道材料時,可提高柵電極控制溝道中載流子傳輸的能力,...

集成電路創新技術