在先進集成電路制造工藝中, 納米環(huán)柵器件(GAA)正取代FinFET成為集成電路中的核心器件。垂直納米環(huán)柵器件由于其在減小標準單元面積、緩解柵極長度限制、提高集成密度和改善寄生電容/電阻等方面具有獨特優(yōu)勢, 成為先進邏輯和DRAM技術方面的重要研究方向。?? ?

微電子所集成電路先導工藝研發(fā)中心朱慧瓏研究團隊于2016年首次提出自對準金屬柵的垂直環(huán)柵納米晶體管并對其進行了系統(tǒng)研究,在器件結構、工藝、集成技術及應用等方面獲得了一系列進展和突破,研發(fā)的VSAFET、 VCNFET、Fe-VSAFET、3D NOR等成果陸續(xù)發(fā)表在國際微電子器件領域的頂級期刊上,并多次作為封面或“編輯特選”文章。?? ?

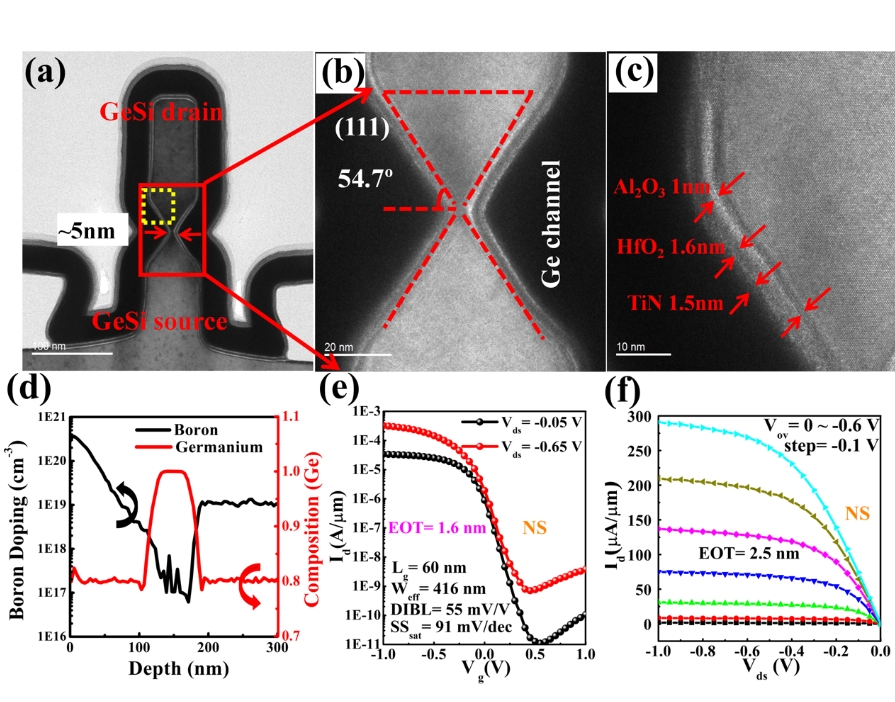

近日,該團隊利用自主研發(fā)的一種自限制ALE (原子層刻蝕) 工藝, 實現(xiàn)了鍺對鍺硅材料和晶面的雙重選擇性精確刻蝕, 制備出了由(111)晶面構成的沙漏型單晶Ge 溝道自對準垂直納米環(huán)柵器件。該沙漏形Ge溝道器件最窄處為5-20nm, 表現(xiàn)出良好的短溝道效應免疫等優(yōu)異性能, 納米線器件的開態(tài)電流 (Ion)達到291 A/ m,為同類器件最大。該器件同時具有較高的電流開關比(Ion/Ioff = 3.1 106), 良好的亞閾值擺幅 (SS = 91 mV/dec)和漏致勢壘降低 (DIBL = 55mV/V)。相關研究成果發(fā)表在工程技術類頂級期刊ACS NANO(2023年影響因子/JCR分區(qū):17.1/Q1)上 (DOI: 10.1021/acsnano.3c02518) , 先導中心博士生謝璐為文章第一作者, 朱慧瓏研究員與張永奎高級工程師為共同通訊作者。?? ?

該研究得到中科院戰(zhàn)略先導專項、中科院青年創(chuàng)新促進會、北京超弦存儲器研究院和國家自然科學基金等項目資助。?? ?

文章鏈接:https://pubs.acs.org/doi/10.1021/acsnano.3c02518?

圖 (a) 具有頸縮溝道厚度~5nm的TiN/HfO2/Al2O3/GeOx柵極堆疊的STEM截面, (b) 沙漏形狀的Ge溝道在 (111) 平面形成交角54.7 , (c) EOT=1.6nm的柵極堆疊的STEM圖像, (d)漏極離子注入尖峰退火后Ge和B的SIMS分布, (e) EOT=1.6nm 的Ge溝道p型垂直環(huán)柵納米線器件的Id-Vg轉移特性曲線, (f) EOT=2.5nm 的Ge溝道p型垂直環(huán)柵納米線器件的典型Id-Vds輸出曲線

集成電路創(chuàng)新技術