近日,中科院微電子研究所集成電路先導工藝研發中心王文武/李永亮課題組在鍺硅高遷移率溝道器件技術與集成工藝研究領域取得了階段性進展。課題組提出了一種在三層應變緩沖層(SRB)上外延鍺硅材料的技術,并通過鍺硅鰭(Fin)刻蝕、新的淺槽隔離(STI)工藝等關鍵模塊研發,成功實現了50%鍺硅Fin的導入集成,為鍺硅高遷移率溝道三維器件的研制提供了技術基礎。

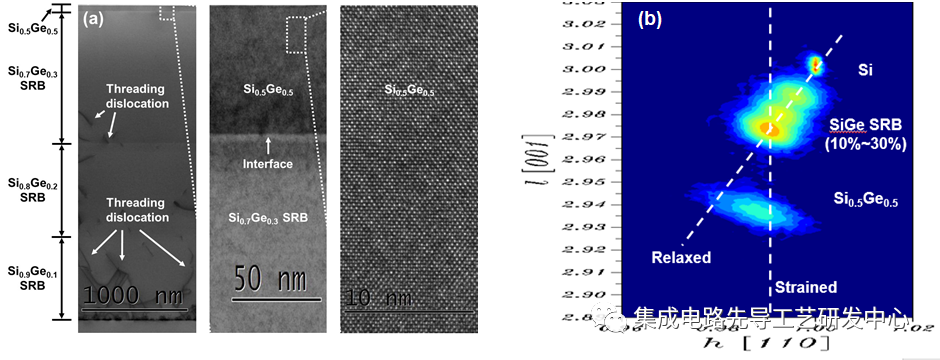

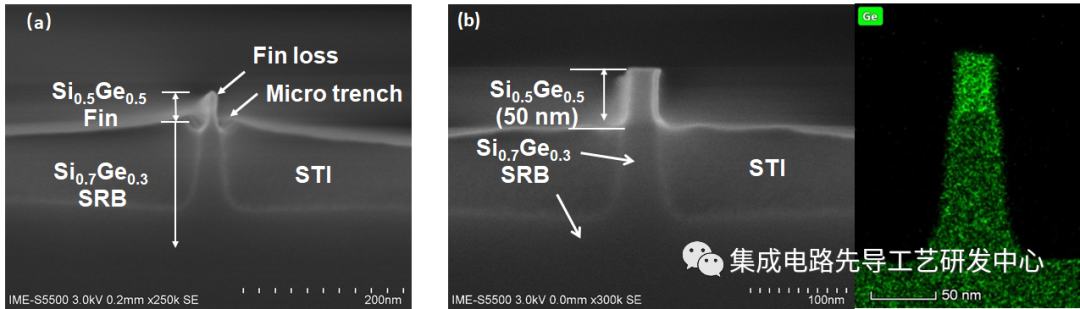

面向集成電路5納米及以下技術節點,鍺硅高遷移率溝道材料因其具有較高的載流子遷移率、更高的器件可靠性以及與現有硅基工藝兼容等特性,成為了新型溝道材料研究的熱點。但是,如果直接在Si襯底上外延鍺硅材料,其關鍵厚度將嚴重限制較高鍺含量的鍺硅材料制備,從而影響器件電學性能的提升。該課題組提出的三層鍺硅SRB結構不僅可以將因晶格失配引起的位錯等晶格缺陷完全限制在SRB中,還能直接提升后續鍺硅溝道層的關鍵厚度。最終,結合平坦化及退火等技術優化,在三層鍺硅SRB上實現了表面粗糙度僅為0.23納米、厚度為50納米、鍺含量為50%的高質量鍺硅材料制備。

圖1 三層SRB/Si0.5Ge0.5疊層結構

(a)TEM分析,(b)倒易空間應力分析

上述成果以“High crystalquality strained Si0.5Ge0.5

圖2 (a)傳統STI last方案,(b)優化方案制備獲得的三層SRB/Si0.5Ge0.5

上述成果以“Fabricationtechnique of the Si0.5Ge0.5

集成電路創新技術