NOR閃存以速度快、可靠性高和使用壽命長等優(yōu)勢,在人工智能、汽車電子和工業(yè)領(lǐng)域中發(fā)揮著不可替代的作用。目前普遍使用的平面NOR閃存在50納米以下技術(shù)代的尺寸微縮遇到瓶頸,難以進(jìn)一步提升集成密度、優(yōu)化器件性能和降低制造成本。為突破上述瓶頸,研究人員提出了多種基于多晶硅溝道的三維NOR(3D NOR)器件,但多晶硅溝道遷移率低、讀取速度慢,影響了NOR器件整體性能。

近日,微電子所集成電路先導(dǎo)工藝研發(fā)中心朱慧瓏研究員團(tuán)隊研發(fā)制備出一種高性能單晶硅溝道3D NOR儲存器。遵循知識產(chǎn)權(quán)保護(hù)優(yōu)先的原則,自2021年起,朱慧瓏在器件結(jié)構(gòu)、集成工藝和電路架構(gòu)等方面先后提出了多個解決方案并提交了相應(yīng)專利申請。該團(tuán)隊使用研發(fā)的垂直晶體管新工藝制備出單晶硅溝道3D NOR三維陣列,其上下疊置的晶體管既具單晶硅溝道的高性能優(yōu)勢,又有三維一體集成的制造成本低的優(yōu)點,可在獲得同等或優(yōu)于單晶硅溝道平面NOR閃存器件性能的同時,無需升級光刻機也可大幅提高存儲器集成密度、增加存儲容量。團(tuán)隊研制的3x3x2三維NOR閃存陣列實現(xiàn)了正常讀寫和擦除,達(dá)到了讀電流以及編程、擦除速度與二維NOR閃存器件相當(dāng)?shù)哪繕?biāo),且新制程與主流硅基工藝兼容,便于應(yīng)用。

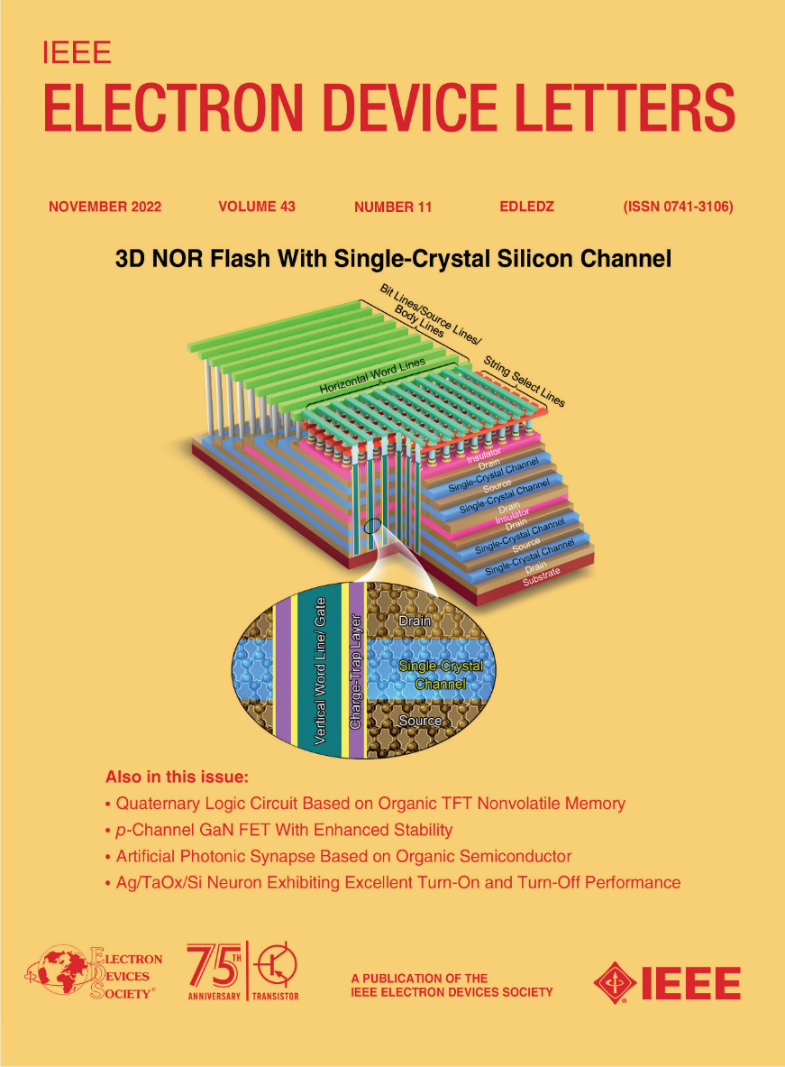

相關(guān)成果作為封面和“編輯特選”(Editors Picks)文章,以題為“A Novel 3D NOR Flash with Single-Crystal Silicon Channel: Devices, Integration, and Architecture”發(fā)表在國際微電子頂刊《IEEE Electron Device Letters》上。微電子所博士研究生黃偉興是第一作者,朱慧瓏為通訊作者,這也是朱慧瓏研究團(tuán)隊的垂直納米器件相關(guān)成果再次入選“編輯特選”文章。

該研究部分得到中國科學(xué)院自主部署項目(Y7YC01X001)的資助。

論文鏈接:https://ieeexplore.ieee.org/document/9906527

圖1.刊登在《Electron Device Letters》封面上的單晶硅3D NOR電路架構(gòu)(上)及垂直溝道晶體管結(jié)構(gòu)(下)

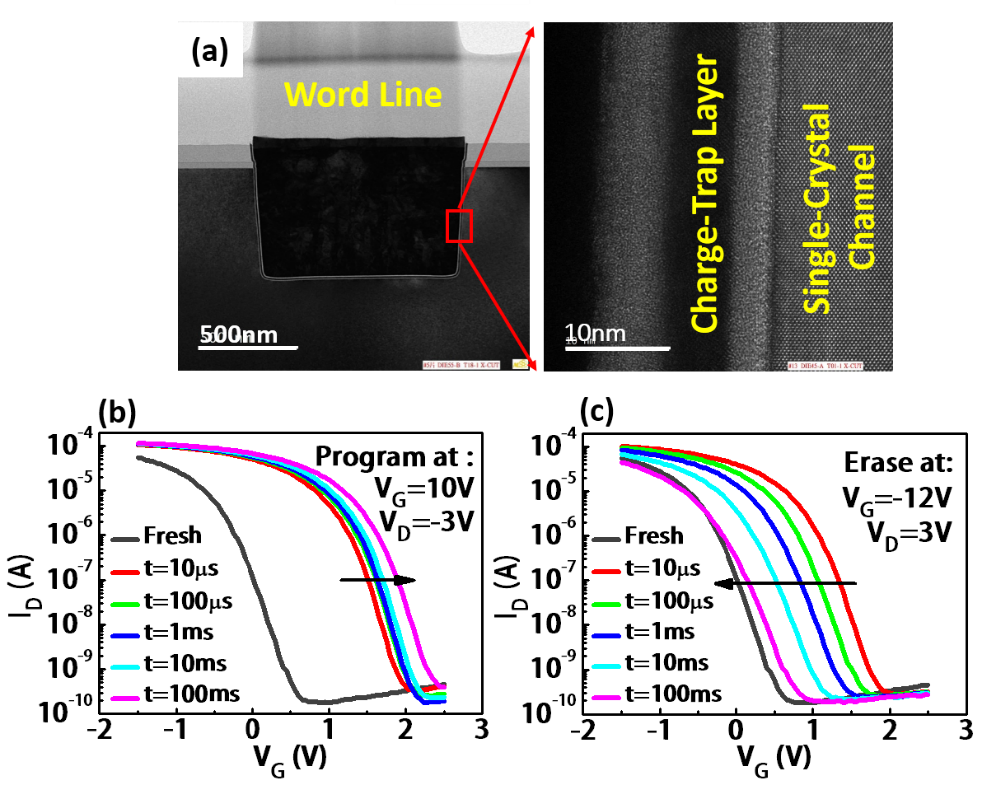

圖2. 單晶硅溝道3D NOR器件及電性實驗結(jié)果:(a)器件TEM截圖(左)及溝道局部放大圖(右),(b)編程特性和(c)擦除特性

| 相關(guān)新聞: |

| 中科院微電子所與華為海思合作在無外磁場寫入的自旋軌道矩磁隧道結(jié)器件的研究中取得新進(jìn)展 |

| 微電子所垂直溝道納米晶體管研發(fā)工作再獲重要突破 |

| 微電子所在無外場單級電壓控制SOT-MTJ自旋邏輯器件的研究中取得新進(jìn)展 |

綜合新聞