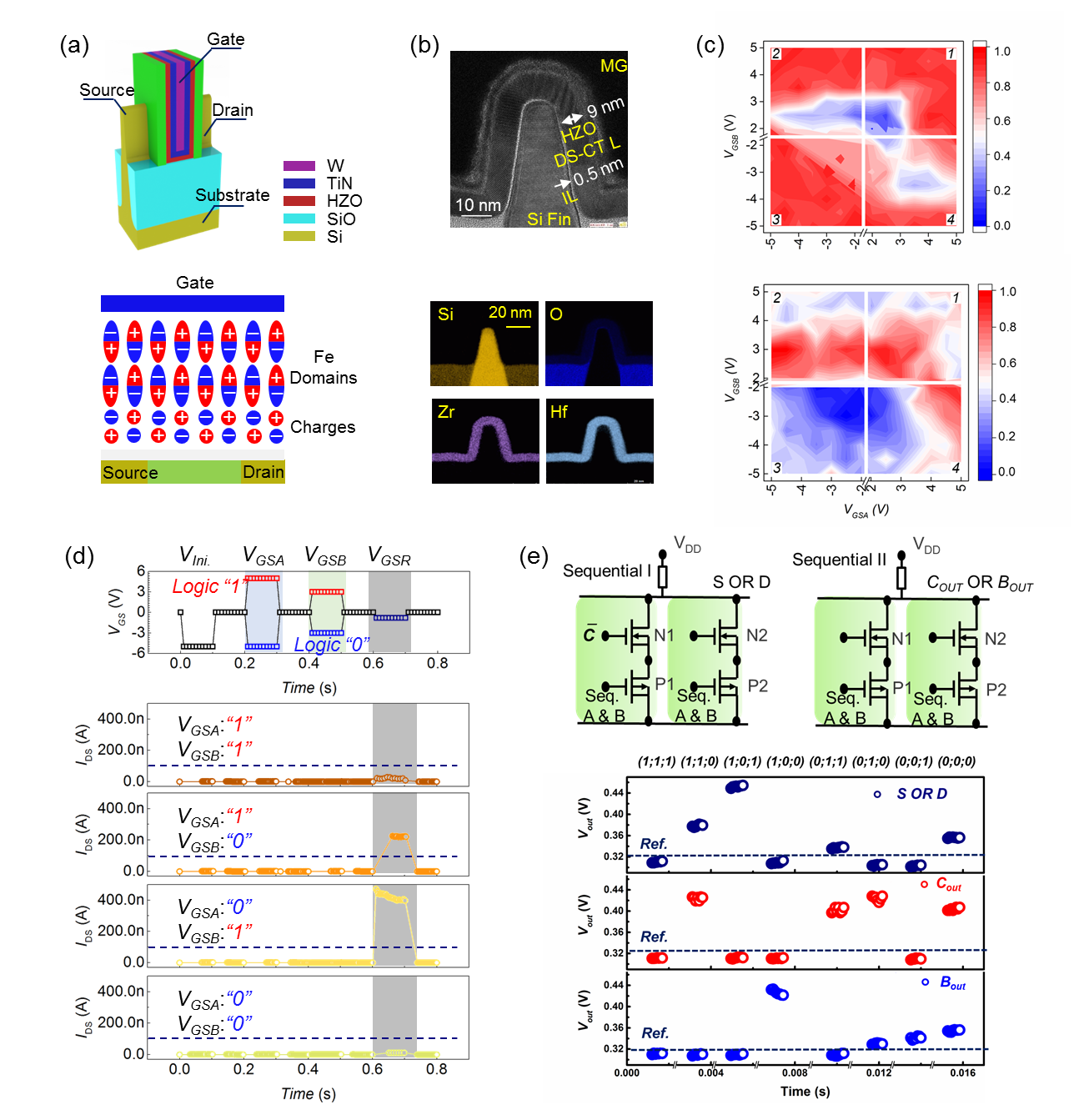

中科院微電子所集成電路先導(dǎo)工藝研發(fā)中心殷華湘研究員團隊提出一種同時實現(xiàn)電荷俘獲(CT)與鐵電極化反轉(zhuǎn)(PS)耦合的新型多模態(tài)Fe-FinFET存算一體器件。通過時域連續(xù)柵壓VGSA與VGSB變化實現(xiàn)晶體管CT與DS空間上的耦合運算,獲得基于Fe-FinFET的單器件(1T)存算一體單元電路。進而通過改變柵壓幅值或脈寬,實現(xiàn)對晶體管CT與DS耦合幅度調(diào)控,獲得不同的溝道電導(dǎo)分布,實現(xiàn)可重構(gòu)的多種布爾邏輯運算。基于此新機制,研究團隊成功在2T單元電路上獲得全部16種布爾邏輯運算,并應(yīng)用該技術(shù),在4T單元上實現(xiàn)了可重構(gòu)的一位加法器和減法器算術(shù)邏輯運算功能。相比基于常規(guī)CMOS晶體管的傳統(tǒng)功能電路(僅加法器需要30T)大幅減小了硬件開銷并顯著提升能效,為未來后摩爾極低功耗器件和電路技術(shù)突破提供了一種創(chuàng)新技術(shù)方案。

該成果近日以“A Polarization-Switching, Charge-Trapping, Modulated Arithmetic Logic Unit for In-Memory Computing Based on Ferroelectric Fin Field-Effect Transistors”為題發(fā)表在國際著名期刊《ACS Applied Materials & Interfaces》上(DOI: 10.1021/acsami.1c20189,中科院一區(qū))。微電子所張兆浩助理研究員為該文第一作者,殷華湘研究員、張青竹副研究員為該文通訊作者。

該研究得到了國家自然科學(xué)基金后摩爾重大研究計劃及青年項目的資助。

圖(a)新型PS-CT多模態(tài)存算一體FinFET器件結(jié)構(gòu)及原理;(b)結(jié)構(gòu)TEM表征圖;(c)p以及n型可重構(gòu)PS-CT存算一體器件在不同VGSA與VGSB輸入組合下獲得的不同溝道電導(dǎo)分布圖;(d)基于1T p型PS-CT FinFET實現(xiàn)XOR布爾邏輯運算的操作方案及電學(xué)結(jié)果;(e)基于4T的可重構(gòu)加/減法器算術(shù)邏輯運算單元構(gòu)建方案及電學(xué)結(jié)果

| 相關(guān)新聞: |

| 微電子所首次亮相CIOE光博會 |

| 微電子所在極紫外光刻基板缺陷補償方面取得新進展 |

綜合新聞