DRAM是存儲器領域最重要的分支之一。隨著尺寸微縮,1T1C結構DRAM的存儲電容限制問題愈發顯著,導致傳統1T1C-DRAM面臨微縮挑戰。基于銦鎵鋅氧(IGZO)晶體管的2T0C-DRAM有望克服1T1C-DRAM的微縮挑戰,在3D DRAM方面發揮更大的優勢。但現階段研究工作都基于平面結構的IGZO器件,形成的2T0C單元尺寸(大約20F2)比相同特征尺寸下的1T1C單元尺寸(6F2)大很多,使得IGZO-DRAM缺少密度優勢。

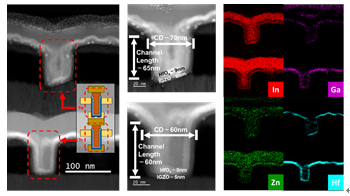

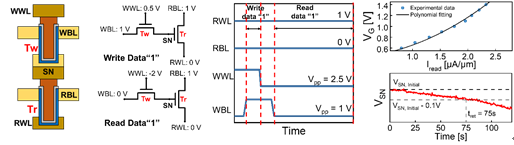

針對平面結構IGZO-DRAM的密度問題,微電子所重點實驗室劉明院士團隊在2021年及2022年IEDM國際大會報道的垂直環形溝道結構(Channel-All-Around, CAA)IGZO晶體管的基礎上,分析了沉積IGZO溝道的ALD工藝對于器件性能及穩定性的調控作用,研究了堆疊第二層IGZO晶體管對第一層器件性能的影響。在此基礎上,第一次成功實現了基于垂直堆疊的CAA IGZO晶體管形成的4F2?2T0C DARM單元。上下兩層的晶體管表現出良好的器件性能和穩定性,得到的2T0C DRAM單元實現了75秒的保持時間,同時進行1011次寫入擦除操作后沒有表現出性能劣化。

該研究成果證明了堆疊CAA IGZO 2T0C結構的可行性,有助于推動IGZO DRAM在三維高密度DRAM中的應用。基于該成果的文章 “First Demonstration of Stacked 2T0C-DRAM Bit-Cell Constructed by Two-Layers of Vertical Channel-All-Around IGZO FETs Realizing 4F2?Area Cost” 入選2023 IEDM。微電子所博士生陳傳科為第一作者,北京超弦存儲器研究院項金娟副研究員為共同第一作者,微電子所李泠研究員、耿玓研究員及北京超弦存儲器研究院趙超研究員、王桂磊研究員為通訊作者。

圖1:由兩個垂直堆疊的CAA IGZO晶體管構成的2T0C單元的截面電鏡圖

圖2:CAA 2T0C單元的retention測試及結果

| 相關新聞: |

| 微電子所在IGZO 2T0C DRAM多值存儲領域取得重要進展 |

| 微電子所在小尺寸獨立雙柵非晶IGZO晶體管緊湊模型領域取得重要進展 |

| 微電子所在鉿基鐵電存儲器芯片研究領域取得重要進展 |

綜合新聞