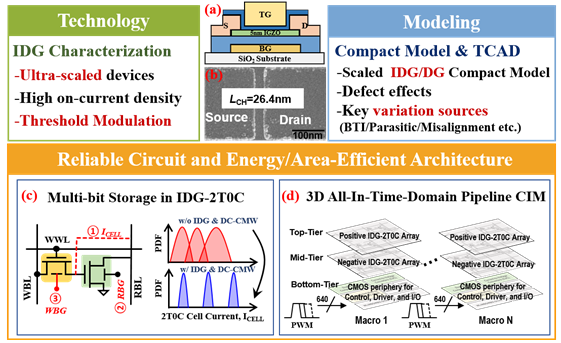

超大規(guī)模獨(dú)立雙柵(IDG)InGaZnO-FET具有低漏電、操作靈活和三維集成的特點(diǎn),有望實(shí)現(xiàn)高能效和高密度的存內(nèi)計(jì)算。但其復(fù)雜的工作原理、增加的變化源和擴(kuò)大的寄生效應(yīng)阻礙了器件建模和電路設(shè)計(jì)。

針對(duì)上述問(wèn)題,開(kāi)發(fā)了一種可靠性感知的緊湊型模型(RaCM),研究了納米級(jí) IDG IGZO TFT 的可靠性問(wèn)題(BTI、多器件閾值電壓波動(dòng)、錯(cuò)位和寄生問(wèn)題)。通過(guò)實(shí)驗(yàn)(LCH~26nm)和 TCAD 校準(zhǔn),提出了一種 IDG-2T0C 多比特計(jì)算單元,它采用二極管連接寫入策略抑制變化,并采用獨(dú)立柵極增強(qiáng)數(shù)據(jù)完整性和保留方案。首次使用 28 納米 Si-CMOS 和 26 納米 IGZO 器件進(jìn)行可靠性感知的混合電路仿真,它實(shí)現(xiàn)了高達(dá) 2766 TOPS/W 的歸一化能效 (EF),和現(xiàn)有技術(shù)相比性能提高了3倍以上,且在1000s之后,CIFAR-10 推理精度損失小于 2%。

基于該成果的文章“Reliability-Aware Ultra-Scaled IDG-InGaZnO-FET Compact Model to Enable Cross-layer Co-design for Highly Efficient Analog Computing in 2T0C-DRAM”入選2023 IEDM。微電子所博士生徐麗華、陳楷飛、李智為共同第一作者,微電子所竇春萌研究員、楊冠華研究員和汪令飛研究員為共同通訊作者。

(a) 獨(dú)立雙柵非晶IGZO晶體管的原理圖和

(b) SEM圖

(c) 實(shí)現(xiàn)IDG-2T0C多值存儲(chǔ)的關(guān)鍵技術(shù)

(d) 三維多比特模擬全時(shí)域CIM 架構(gòu)圖

| 相關(guān)新聞: |

| 微電子所在鉿基鐵電存儲(chǔ)器芯片研究領(lǐng)域取得重要進(jìn)展 |

| 微電子所在三維鐵電存儲(chǔ)器噪聲特性應(yīng)用方面取得進(jìn)展 |

| 微電子所在阻變存儲(chǔ)器芯片創(chuàng)新應(yīng)用研究取得進(jìn)展 |

學(xué)習(xí)園地