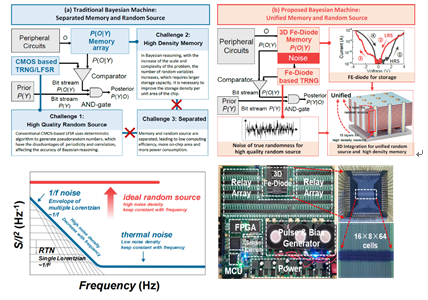

傳統(tǒng)貝葉斯機(jī)面臨三大挑戰(zhàn):一是需要高質(zhì)量的隨機(jī)源生成具有真隨機(jī)性的隨機(jī)比特?cái)?shù)流;二是由于隨機(jī)變量隨著問(wèn)題的規(guī)模和復(fù)雜度的增加而增加,因此需要高密度的存儲(chǔ)器;三是存儲(chǔ)器和隨機(jī)源的分離,導(dǎo)致了芯片面積和功耗的浪費(fèi)。

針對(duì)這些挑戰(zhàn),微電子所劉明院士團(tuán)隊(duì)首次構(gòu)建了存儲(chǔ)器和隨機(jī)源融合的貝葉斯機(jī)。通過(guò)16層3D集成Fe-Diode實(shí)現(xiàn)了極高的存儲(chǔ)密度(0.26F2/bit);此外,通過(guò)對(duì)Fe-Diode器件的噪聲行為的系統(tǒng)研究,發(fā)現(xiàn)了與頻率無(wú)關(guān)的高噪聲密度的散粒噪聲(shot noise),并利用該噪聲作為隨機(jī)源,生成了自相關(guān)性接近零的隨機(jī)比特?cái)?shù)流;進(jìn)一步通過(guò)將存儲(chǔ)器和隨機(jī)源統(tǒng)一在16層3D Fe-Diode陣列中實(shí)現(xiàn)了該貝葉斯機(jī)。

通過(guò)對(duì)比發(fā)現(xiàn),本工作在比特?cái)?shù)流長(zhǎng)度為15時(shí),可以實(shí)現(xiàn)95.31%的MNIST識(shí)別精度。與基于線(xiàn)性反饋移位寄存器相比,識(shí)別精度提升了9.37%。同時(shí),本工作具備高噪聲容忍能力,在10%的外部噪聲下,精度僅下降了8.75%。

該研究成果以題為“First Demonstration of a Bayesian Machine based on Unified Memory and Random Source Achieved by 16-layer Stacking 3D Fe-Diode with High Noise Density and High Area Efficiency”入選2023 IEDM。微電子所龔天成副研究員為第一作者,復(fù)旦大學(xué)博士生胡啟樵為共同一作,微電子所楊建國(guó)副研究員和羅慶研究員為通訊作者。

圖 基于三維16層Fe-Diode器件的貝葉斯機(jī)

| 相關(guān)新聞: |

| 微電子所在阻變存儲(chǔ)器芯片創(chuàng)新應(yīng)用研究取得進(jìn)展 |

| 微電子所在面向存內(nèi)計(jì)算的多比特2T0C DRAM研究中取得重要進(jìn)展 |

| 微電子所在氮化鎵器件可靠性及熱管理研究方面取得重要進(jìn)展 |

學(xué)習(xí)園地