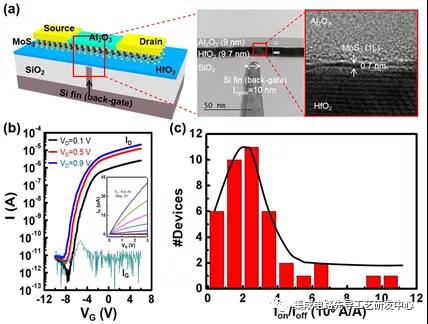

近期,中國科學院微電子研究所集成電路先導工藝研發中心在新型二維材料器件面向未來集成電路集成應用研發中取得重要進展,結合硅基FinFET工藝成功研制出10nm超短物理柵長二硫化鉬晶體管,實現電流開關比達到107。

二維半導體材料具有原子級的厚度,被用作晶體管的溝道材料時,可提高柵電極控制溝道中載流子傳輸的能力,從而抑制晶體管的短溝道效應。國際半導體路線圖預測在1納米以下節點,二維材料是延續摩爾定律的重要候選者之一。但由于微納加工技術的限制,很難大規模制備超短柵長的二維材料晶體管,這使二維材料在集成電路產業化應用方面面臨嚴重挑戰。先導中心殷華湘研究員的團隊在主流硅基FinFET集成工藝的基礎上,巧妙利用了納米級寬度的三維立體鰭型硅作為晶體管背柵電極,并集成單原子層厚度的二硫化鉬薄膜作為溝道材料,成功研制出高電流開關比的10nm柵長二硫化鉬晶體管(最大Ion/Ioff = 1×107)。與此同時,采用傳統的硅基集成技術“自對準側墻轉移法”制備的鰭型硅背柵電極,其優點為可圖形化、大規模、陣列式制備,搭配CVD方法生長的厘米尺寸單層二硫化鉬溝道材料,可同時制備出幾百個10 nm柵長晶體管,測試發現有85%的器件電流開關比高于106,這也是首次對10 nm柵長二硫化鉬晶體管進行統計性電學測試,標志著微電子所在新型二維材料器件面向集成電路規模集成的研發方面取得了重要進展。

該研究結果已發表在《IEEE Journal of theElectron Devices Society》上(DOI:10.1109/JEDS.2019.2910271),并已申請專利保護(專利號:201810134787.9)。該項新技術研究得到了國家重點研發計劃納米專項的項目資助。

圖 1 (a)10nm柵長二硫化鉬晶體管的結構示意圖和TEM表征;(b)器件的轉移特性曲線;(c)器件的電流開關比分布統計圖。

| 相關新聞: |

| STT-MRAM器件與集成技術研究 |

| 鍺硅高遷移率溝道器件技術與集成工藝研發階段性進展 |

學習園地