物聯網與人工智能技術的迅猛發展對邊緣節點計算平臺的實時數據處理能力與能效提出了更高要求。基于新型存儲器的非易失存內計算技術可實現數據的原位存儲與計算、將數據搬運帶來的功耗與延遲開銷最小化,從而大幅提升邊緣設備的數據處理能力與效能比。但由于基礎單元特性的非理想因素,陣列中的寄生效應以及模數轉換電路的硬件開銷,非易失存內計算仍面臨計算性能與能效方面的限制。?

圍繞上述關鍵問題,微電子所劉明院士團隊采用跨層次協同設計的方法,提出了高并行與高效能比的新型RRAM存內計算結構。?

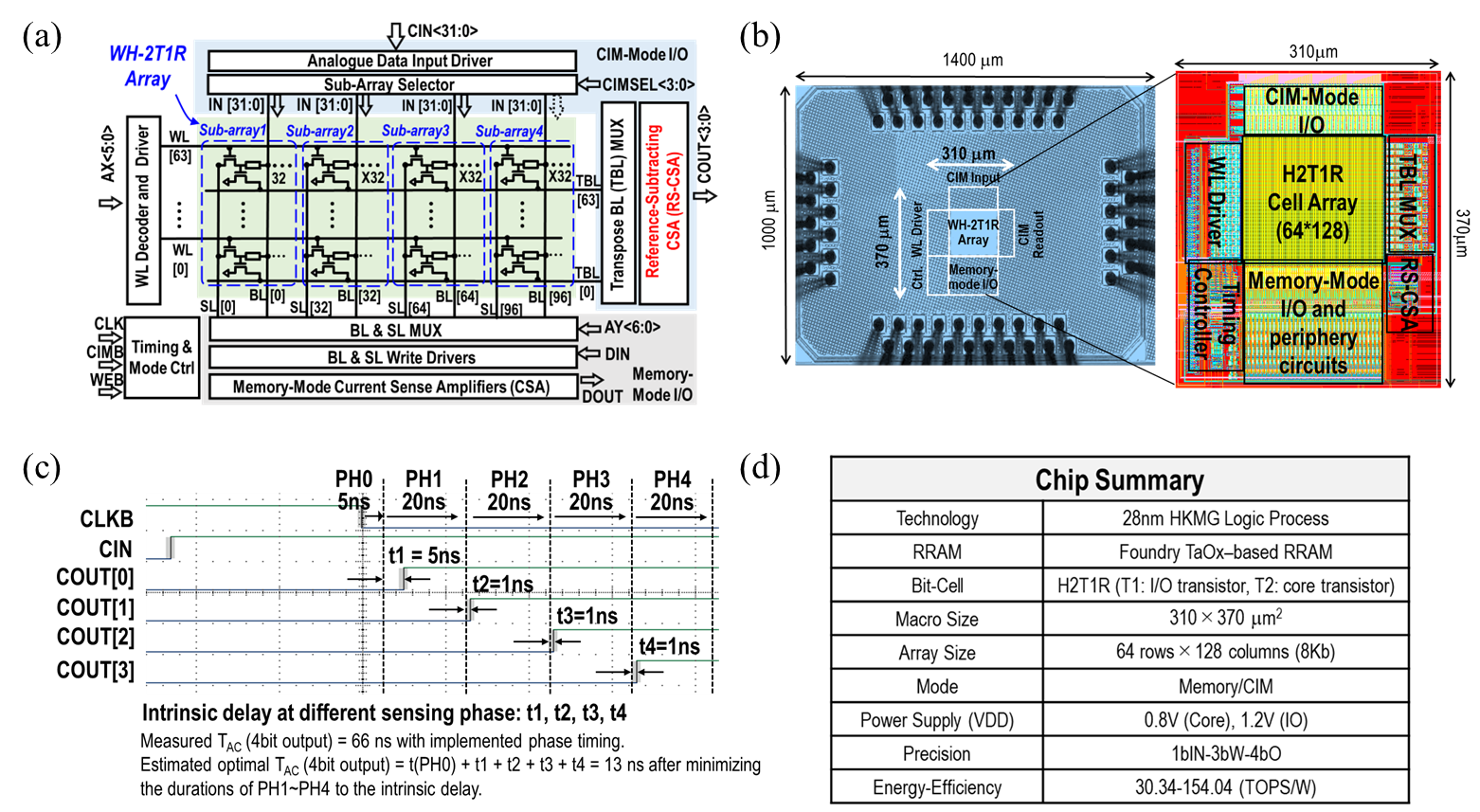

在器件層面,研究團隊提出了帶權重二晶體管一憶阻器(WH-2T1R)的存算陣列結構。WH-2T1R結構使用core晶體管構成解耦的存算數據通路來減小寄生效應對計算電流的影響,相較1T1R結構只額外造成30.3%的面積開銷。計算單元利用第二晶體管亞閾值區放大特性提高計算13.5倍開關比的同時降低88%的低阻態計算電流,從而實現了63.4%的乘加操作功耗降低。得益于計算開關比的提升,該RRAM存內計算結構可支持更高的輸入并行度和多比特乘加操作。?

在電路層面,研究團隊提出了參考電流減式電流型靈敏放大器的讀出電路。由參考電流減支路根據上一次讀出結果先對輸入電流進行電流減再送到電流鏡讀出數據。參考電流減支路對半減小了電流鏡輸入電流范圍,使RRAM存算結構支持的計算電流范圍倍增,能實現更高輸入并行和多比特乘加,并取得79.5%的讀出電路功耗降低。研究團隊通過進一步優化電流型靈敏放大器電流減配置,實現積分非線性誤差5倍提升,微分非線性誤差3.75倍提升。?

在算法映射層面,研究團隊提出了高位數據冗余(MSB_RSM)的映射策略。RRAM存內計算結構配備有不同第二晶體管multiplier參數的多組陣列和額外的一組冗余陣列。其中不同第二晶體管用于映射多比特權值的不同比特位。由于RRAM和晶體管非理想因素對計算電流的影響不容忽視,冗余陣列用于額外映射權值對非理想因素補償。經過對不同比特位補償效果的分析,MSB-RSM對高位權值進行操作時能減小1σ誤差40%。得益于更穩定的計算電流,在ResNet-18模型下的CIFAR-10和CIFAR-100任務獲得了0.96%和2.83%的準確度提升。?

上述方案在團隊自主開發的嵌入式28nm 工藝上得到驗證,新型RRAM存內計算結構支持高并行的模擬域乘加操作,在1比特輸入、3比特權值、4比特輸出下ResNet-18任務中的平均能效達到30.34TOPS/W,并可以通過進一步優化讀出時序提升到154.04TOPS/W。該工作通過單元、電路及系統面的系統設計,為高能效、高精度的模擬存內計算提供了新思路。?

研究成果以“A 28nm RRAM Computing-in-Memory Macro Using Weighted Hybrid 2T1R Cell Array and Reference Subtracting Sense Amplifier for AI Edge Inference”為題發表在集成電路設計領域旗艦期刊IEEE Journal of Solid-State Circuits上,微電子所博士研究生葉望為該文章的第一作者、竇春萌研究員為該文章的通訊作者。?

?

?

(a)基于RRAM的存內計算芯片結構框圖,(b)芯片晶圓照片及版圖,

(c)芯片測試數字波形,(d)芯片參數

| 相關新聞: |

| 微電子所在鐵電存儲器可靠性研究方面取得進展 |

| 微電子所在單細胞電學特性流式分析方法及分析儀器研究方面取得新進展 |

| 微電子所在氧化鉿基鐵電存儲材料方面取得重要進展 |

綜合新聞