垂直堆疊納米線/納米片全包圍柵(Gate All Around, GAA)互補場效應(yīng)晶體管(Complementary Field Effect Transistor,CFET),將不同導(dǎo)電溝道類型(N-FET和P-FET)的GAA器件在垂直方向進行高密度三維單片集成。相較于現(xiàn)有主流FinFET與水平GAA晶體管集成電路工藝,CFET突破了傳統(tǒng)N/P-FET共平面布局間距的尺寸限制,可將集成電路中邏輯標準單元尺度微縮到4-T(Track)高度,同時將減少SRAM單元面積40%以上,在3納米以下技術(shù)代高密度、高性能集成電路制造技術(shù)中將成為基礎(chǔ)晶體管器件創(chuàng)新架構(gòu)的有力候選者。

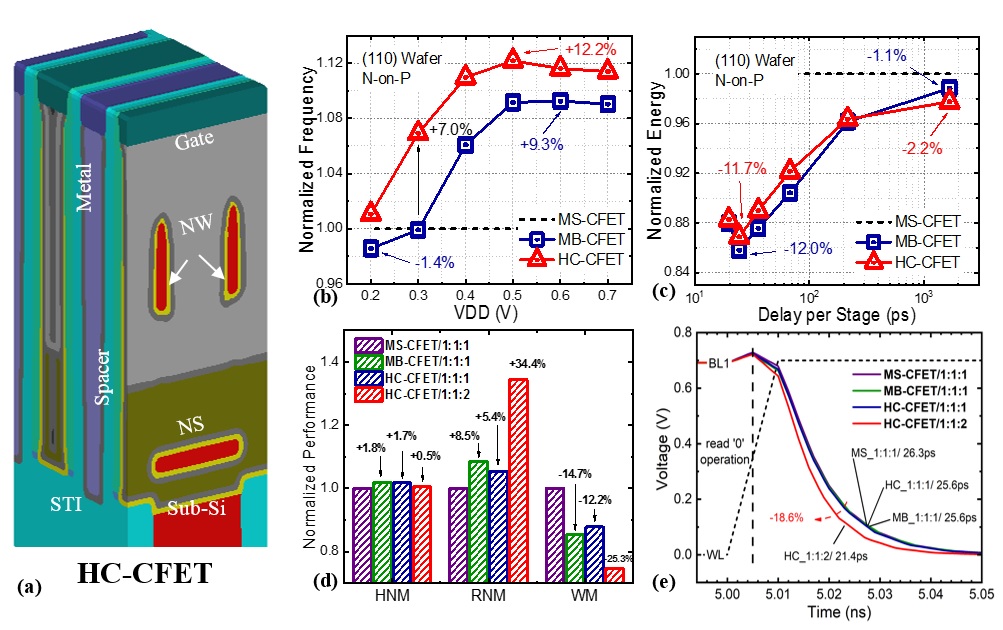

近日,微電子所集成電路先導(dǎo)工藝研發(fā)中心殷華湘/吳振華研究團隊利用業(yè)界主流的Design-Technology Co-optimization(DTCO)方法全面探索了CFET的器件架構(gòu)優(yōu)勢,提出了新型混合溝道CFET(Hybrid Channel Complementary FET,HC-CFET)結(jié)構(gòu)設(shè)計和集成方案。該結(jié)構(gòu)能夠在單一襯底上,不借助晶圓鍵合等混合晶向技術(shù),利用SiNx與SiO2的高刻蝕選擇比,通過分步溝道形貌刻蝕,實現(xiàn)對N-FET和P-FET首選高電子與空穴遷移率導(dǎo)電溝道的共同優(yōu)化,即使得N-FET具有(100)溝道表面晶向,P-FET具有(110)溝道表面晶向,從而在同等投影平面下獲得最佳的器件與電路性能。該結(jié)構(gòu)設(shè)計與集成方案的可行性已通過Virtual-FAB模擬仿真驗證。進一步通過精確數(shù)值求解預(yù)測了全部寄生參數(shù),對比了不同CFET架構(gòu)下的17級環(huán)形振蕩器和SRAM單元性能。結(jié)果表明,相較于常規(guī)垂直集成Fin和垂直集成納米片的CFET結(jié)構(gòu)(MS-CFET和MB-CFET),新型HC-CFET具有溝道晶向與空間布局優(yōu)勢,展現(xiàn)出更高的工作頻率以及更優(yōu)的噪聲容限窗口,以及在高度微縮的高性能CMOS集成電路應(yīng)用上的巨大潛力。

該成果近日以“Investigation of Novel Hybrid Channel Complementary FET Scaling Beyond 3-nm Node From Device to Circuit”為題發(fā)表在《電氣和電子工程師協(xié)會電子器件學(xué)報》期刊上(IEEE Transactions on Electron Devices 69, 3581 (2022), DOI: 10.1109/TED.2022.3176843),微電子所博士生羅彥娜為該文章第一作者。微電子所殷華湘研究員、吳振華研究員為該文通訊作者。該項研究得到中國科學(xué)院“戰(zhàn)略重點研究計劃”、國家自然科學(xué)基金委、北京市科委科技計劃等項目的支持。(原文鏈接:https://ieeexplore.ieee.org/document/9789149)

(a) HC-CFET結(jié)構(gòu)示意圖,以及仿真對比的17級環(huán)形振蕩器(b)歸一化頻率特性和(c)歸一化能耗特性與6T-SRAM單元(d)歸一化噪聲容限特性和(e)讀操作瞬態(tài)特性

| 相關(guān)新聞: |

| 單原子層溝道的鰭式場效應(yīng)晶體管問世 |

| 單原子層溝道的鰭式場效應(yīng)晶體管問世 |

| 開發(fā)超低功耗黑磷隧道場效應(yīng)晶體管延續(xù)摩爾定律 |

綜合新聞