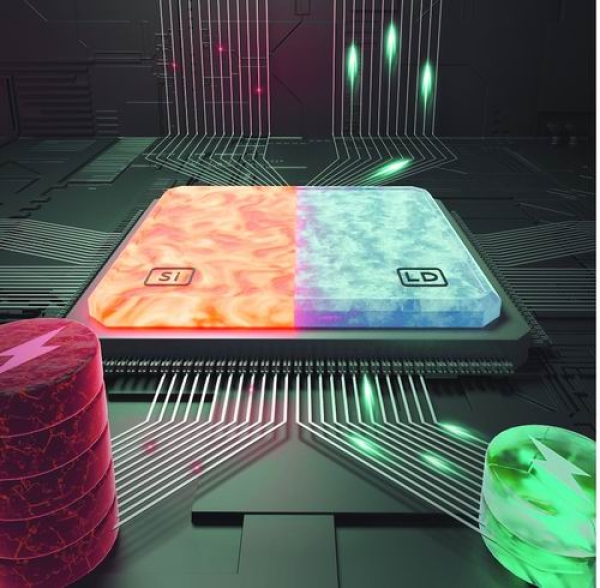

更快、更省電的低維半導(dǎo)體芯片。受訪者供圖

隨著硅基芯片逐漸接近摩爾定律物理極限,科學(xué)界和產(chǎn)業(yè)界都在不斷嘗試?yán)酶鞣N二維材料,開(kāi)發(fā)出更優(yōu)秀的新一代芯片。

近日,北京大學(xué)電子學(xué)院彭練矛院士、邱晨光研究員團(tuán)隊(duì)研發(fā)出彈道二維硒化銦(InSe)晶體管,這是世界上迄今速度最快、能耗最低的二維半導(dǎo)體晶體管,其實(shí)際性能超過(guò)英特爾商用最先進(jìn)的硅基晶體管。相關(guān)研究近日發(fā)表于《自然》。

據(jù)介紹,新晶體管室溫彈道率達(dá)83%,遠(yuǎn)高于硅基晶體管的彈道率(低于60%),有望實(shí)現(xiàn)兼具高性能和低功耗的芯片。“在彈道輸運(yùn)晶體管中,電子像子彈一樣穿過(guò)溝道沒(méi)有受到碰撞,能量沒(méi)有散射損失,所以彈道率越高的器件,能量利用效率越高。”邱晨光告訴《中國(guó)科學(xué)報(bào)》。

多位國(guó)際審稿人認(rèn)為,這項(xiàng)研究解決了實(shí)現(xiàn)高性能二維晶體管的多個(gè)重要挑戰(zhàn),是二維電子器件研究的重要里程碑,具有重要的科學(xué)意義。

瞄準(zhǔn)關(guān)鍵瓶頸

芯片作為信息時(shí)代的“心臟”,為大數(shù)據(jù)和人工智能的發(fā)展提供源源不斷的動(dòng)力。芯片速度的提升得益于晶體管的微縮,然而,當(dāng)前硅基芯片已接近摩爾定律物理極限。

計(jì)算機(jī)行業(yè)一直遵循著摩爾定律,即當(dāng)價(jià)格不變時(shí),在給定的集成電路面積上,容納比前一代多一倍的晶體管,使其性能提升一倍。但多年來(lái)的實(shí)踐表明,集成電路在性能提升的同時(shí),短溝道效應(yīng)等負(fù)面效應(yīng)相應(yīng)增加,集成難度、能耗和成本也在提高。

二維半導(dǎo)體材料被認(rèn)為是芯片溝道材料的下一個(gè)“風(fēng)口”。

這種原子級(jí)厚度的材料具有超薄體、高遷移率等優(yōu)勢(shì),引起了科學(xué)界和工業(yè)界的廣泛興趣。近年來(lái),英特爾、臺(tái)積電、三星和歐洲微電子研究中心等全球領(lǐng)先的半導(dǎo)體制造公司與研究機(jī)構(gòu)均對(duì)二維材料展開(kāi)了研究。

然而,由于接觸電阻、柵介質(zhì)等方面的瓶頸,迄今為止,所有二維晶體管所實(shí)現(xiàn)的性能均不能媲美業(yè)界先進(jìn)的硅基晶體管。

基于10多年來(lái)在納米器件領(lǐng)域的研究,北大團(tuán)隊(duì)針對(duì)二維電子學(xué)領(lǐng)域的底層核心問(wèn)題和關(guān)鍵科學(xué)瓶頸進(jìn)行攻關(guān),希望挖掘二維半導(dǎo)體在電子學(xué)領(lǐng)域的最終潛力,制備出真正發(fā)揮低維材料本征優(yōu)勢(shì)的二維晶體管。

他們選用二維硒化銦作為溝道材料,這種半導(dǎo)體材料具備遠(yuǎn)超同類(lèi)材料的絕佳物理特性。例如,擁有更高的室溫載流子遷移率、更小的電子有效質(zhì)量,材料本征的熱速度更高。根據(jù)計(jì)算,其電學(xué)性能優(yōu)于目前已知的幾乎全部的N型半導(dǎo)體材料(包括傳統(tǒng)的硅半導(dǎo)體)。

“理論上,用二維硒化銦作為溝道的晶體管擁有更高的極限性能。”論文第一作者、北京大學(xué)電子學(xué)院博士生姜建峰對(duì)《中國(guó)科學(xué)報(bào)》說(shuō)。

然而,如何讓理論成為現(xiàn)實(shí)?這并非易事。

硒化銦等二維半導(dǎo)體材料應(yīng)用方面的一個(gè)國(guó)際難題是,這類(lèi)材料與金屬接觸會(huì)形成“費(fèi)米釘扎效應(yīng)”,產(chǎn)生大接觸電阻,極大限制了晶體管的速度。

“彈道晶體管在超短溝道傳輸時(shí)幾乎沒(méi)有散射,能量主要消耗在接觸處的金屬與半導(dǎo)體結(jié)中,這是二維電子學(xué)中的核心瓶頸。”邱晨光說(shuō)。

面對(duì)這一難題,研究團(tuán)隊(duì)通過(guò)總結(jié)和考察商用硅基晶體管接觸方面的成熟結(jié)構(gòu)與策略,探索出一種在二維電子器件中實(shí)現(xiàn)歐姆接觸的全新方法,即固態(tài)源摻雜誘導(dǎo)相變技術(shù),在全球率先將二維晶體管的器件總電阻推至接近理論極限,刷新至124歐姆·微米,滿足集成電路未來(lái)節(jié)點(diǎn)對(duì)晶體管電阻的要求。

審稿人對(duì)這一技術(shù)革新給予了高度評(píng)價(jià)。他們認(rèn)為,接觸電阻一直是二維半導(dǎo)體電子產(chǎn)品發(fā)展的一個(gè)主要瓶頸,研究者創(chuàng)新性地探索出新方法克服了這個(gè)重大挑戰(zhàn),實(shí)現(xiàn)了創(chuàng)紀(jì)錄的低接觸電阻,為高性能二維晶體管樹(shù)立了標(biāo)桿。

打破硅基芯片終極“紅墻”

國(guó)際半導(dǎo)體器件與系統(tǒng)路線圖(IRDS)預(yù)測(cè),硅基晶體管的極限柵長(zhǎng)為12納米,工作電壓不能小于0.6伏。這定義了未來(lái)硅基芯片縮放過(guò)程結(jié)束時(shí)的最終集成度和功耗。

對(duì)標(biāo)業(yè)界IRDS所預(yù)測(cè)的硅基器件發(fā)展路線圖,邱晨光表示,彈道二維硒化銦晶體管打破了4個(gè)硅基終極“紅墻”。

首先,二維硒化銦晶體管溝長(zhǎng)縮小至10納米,超越硅基極限12納米,器件關(guān)態(tài)特性超過(guò)英特爾商用10納米節(jié)點(diǎn)的硅基最優(yōu)FinFET晶體管。其次,工作電壓可降到0.5伏,超越2031年預(yù)計(jì)的硅基極限0.6伏。再次,門(mén)延時(shí)縮短到0.32皮秒,相當(dāng)于硅基極限(1.26皮秒)的1/4。最后,功耗延遲積縮減到4.32 ×10-29焦秒/微米,比硅基極限低一個(gè)量級(jí)。

姜建峰向《中國(guó)科學(xué)報(bào)》表示,這意味著未來(lái)利用硒化銦晶體管構(gòu)建的大規(guī)模集成電路,在低數(shù)倍功耗的條件下比硅基電路具備更高的性能和處理速度,有望實(shí)現(xiàn)兼具高性能和低功耗的芯片。

“這無(wú)疑是迄今為止性能最高的二維晶體管,說(shuō)明二維材料晶體管的真實(shí)性能(不僅僅在理論上)已經(jīng)超過(guò)了最先進(jìn)的硅基晶體管。”審稿人表示。

開(kāi)啟電子器件“新里程”

這項(xiàng)“里程碑”式的突破帶來(lái)的技術(shù)革新是多方面的。

除解決電子器件總電阻方面的國(guó)際難題外,研究團(tuán)隊(duì)還創(chuàng)新性地采用高載流子熱速度(更小有效質(zhì)量)的三層硒化銦作為溝道,使室溫彈道率高達(dá)83%,遠(yuǎn)高于硅基晶體管的彈道率(低于60%),為目前場(chǎng)效應(yīng)晶體管的最高值。

他們還解決了二維材料表面生長(zhǎng)超薄氧化層的難題,制備出2.6納米的超薄雙柵氧化鉿。

邱晨光表示,接下來(lái),研究團(tuán)隊(duì)將聚焦二維電子學(xué)的幾個(gè)重要研究方向進(jìn)行攻關(guān),如二維器件的P型歐姆接觸、二維材料的晶圓級(jí)單晶的大面積生長(zhǎng)與轉(zhuǎn)移、二維器件的標(biāo)準(zhǔn)化集成加工工藝及其與硅基和碳基的異構(gòu)集成等,從而加速推動(dòng)二維材料芯片技術(shù)的發(fā)展進(jìn)程。

相關(guān)論文信息:https://doi.org/10.1038/s41586-023-05819-w

| 相關(guān)新聞: |

| 二維拓?fù)洳牧蟽?nèi)發(fā)現(xiàn)新奇電子效應(yīng) |

| 工業(yè)硅片上長(zhǎng)出“完美”二維超薄材料 |

| 二維材料成功集成到硅微芯片內(nèi) |

學(xué)習(xí)園地