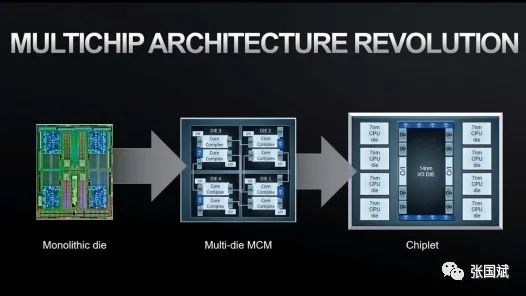

隨著半導(dǎo)體工藝尺寸進(jìn)一步縮小,集成電路制造面臨的挑戰(zhàn)日益增大,摩爾定律日趨放緩,所以Chiplet概念應(yīng)運(yùn)而生,Chiplet就是通過(guò)工藝的改進(jìn)來(lái)解決“摩爾定律”失效的一種方法,Chiplet走向了和傳統(tǒng)的片上系統(tǒng)(SOC)完全不同的道路,類似于搭建樂(lè)高積木,通過(guò)一組小芯片混搭成“類樂(lè)高”的組件。Chiplet技術(shù)是SoC集成發(fā)展到一定程度之后的一種新的芯片設(shè)計(jì)方式,它通過(guò)將SoC分成較小的裸片(Die),再將這些模塊化的小芯片(裸片)互聯(lián)起來(lái),采用新型封裝技術(shù),將不同功能不同工藝制造的小芯片封裝在一起,成為一個(gè)異構(gòu)集成芯片。

其實(shí),Chiplet的概念早在10多年前就被提出了,Chiplet技術(shù)的概念源于號(hào)稱印尼神童的Marvell 創(chuàng)始人周秀文博士提出Mochi架構(gòu) ,他在ISSCC2015的大會(huì)上提出了這個(gè)概念,希望Mochi成為許多應(yīng)用的基礎(chǔ)架構(gòu)。幾年后,這個(gè)概念開(kāi)花結(jié)果,就是現(xiàn)在的Chiplet。

使用Chiplet的好處很多,因?yàn)橄冗M(jìn)制程成本非常高昂,特別是模擬電路、I/O 等愈來(lái)愈難以隨著制程技術(shù)縮小,而Chiplet 是將電路分割成獨(dú)立的小芯片,并各自強(qiáng)化功能、制程技術(shù)及尺寸,最后整合在一起,以克服制程難以微縮的挑戰(zhàn)。此外,基于Chiplet還可以使用現(xiàn)有的成熟芯片降低開(kāi)發(fā)和驗(yàn)證成本。

IBM、英特爾、AMD等都是Chiplet的擁躉,AMD 的EPYC 處理器通過(guò)Chiplet成功實(shí)現(xiàn)了集成64核的高性能服務(wù)器芯片,英特爾的Intel Stratix 10 GX 10M FPGA 也是采用了Chiplet技術(shù)。

2019年以后,Chiplet技術(shù)快速發(fā)展,更多公司開(kāi)始看好這個(gè)技術(shù),臺(tái)積電、日月光、格芯等晶圓廠封測(cè)廠也開(kāi)始支持Chiplet技術(shù),本土也也有很多IC公司如芯原股份等都開(kāi)始提供Chiplet設(shè)計(jì)服務(wù),但是Chiplet還需要解決一個(gè)最大的挑戰(zhàn),那就是標(biāo)準(zhǔn)問(wèn)題,有了一個(gè)公開(kāi)的開(kāi)放標(biāo)準(zhǔn),才可以讓更多公司用起來(lái)。

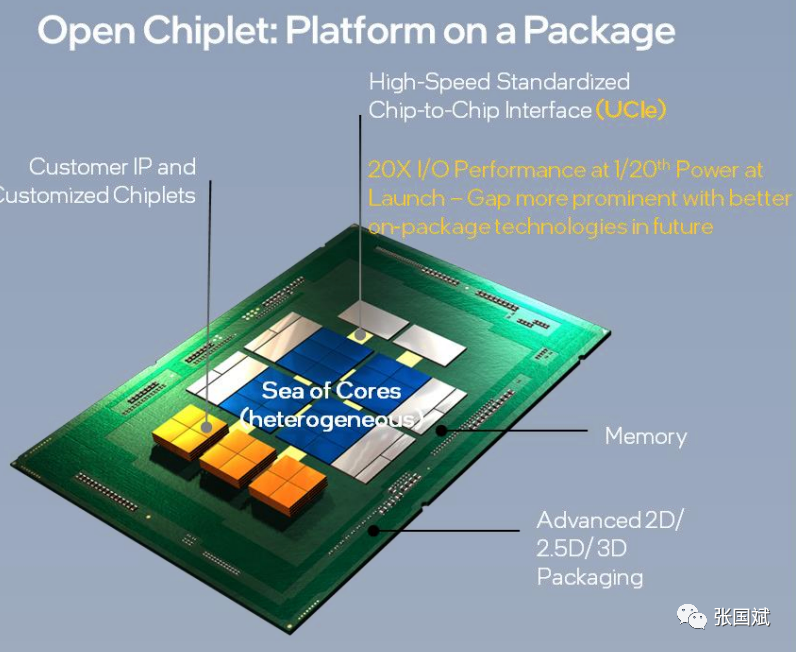

昨天,關(guān)于Chiplet最大的挑戰(zhàn)---Chiplet國(guó)際標(biāo)準(zhǔn)來(lái)了!3月2日,半導(dǎo)體十巨頭ASE、AMD、ARM、Google云、Intel、Meta(Facebook)、微軟、高通、三星、臺(tái)積電十大行業(yè)巨頭聯(lián)合宣布,成立行業(yè)聯(lián)盟,共同打造Chiplet互連標(biāo)準(zhǔn)、推進(jìn)開(kāi)放生態(tài),并制定了標(biāo)準(zhǔn)規(guī)范“UCIe”。UCIe標(biāo)準(zhǔn)的全稱為“Universal Chiplet Interconnect Express”,在芯片封裝層面確立互聯(lián)互通的統(tǒng)一標(biāo)準(zhǔn)。

UCIe是一個(gè)開(kāi)放的工業(yè)標(biāo)準(zhǔn)互連,提供高帶寬、低延遲、高功率和高成本效益的芯片封裝連接。芯片之間的連接。它解決了整個(gè)計(jì)算連續(xù)體中對(duì)計(jì)算、內(nèi)存、存儲(chǔ)和連接的預(yù)期增長(zhǎng)需求。它可以滿足整個(gè)計(jì)算連續(xù)體中不斷增長(zhǎng)的計(jì)算、內(nèi)存、存儲(chǔ)和連接需求,涵蓋云、邊緣、企業(yè)、5G、汽車。高性能計(jì)算和手持設(shè)備領(lǐng)域。

UCIe提供了對(duì)來(lái)自不同來(lái)源的芯片進(jìn)行封裝的能力,包括不同的晶圓廠,以及不同的技術(shù)。不同的來(lái)源,包括不同的工廠、不同的設(shè)計(jì)和不同的封裝技術(shù)。UCIe是行業(yè)領(lǐng)導(dǎo)者共同開(kāi)發(fā)一個(gè)共同標(biāo)準(zhǔn)的結(jié)果。UCIe推動(dòng)者涵蓋了云計(jì)算、半導(dǎo)體制造、OSAT、IP供應(yīng)商和芯片設(shè)計(jì)者的廣泛交集。

UCIe1.0標(biāo)準(zhǔn)定義了芯片間I/O物理層、芯片間協(xié)議、軟件堆棧等,并利用了PCIe、CXL兩種成熟的高速互連標(biāo)準(zhǔn)。該標(biāo)準(zhǔn)最初由Intel提議并制定,后開(kāi)放給業(yè)界,共同制定而成。UCIe標(biāo)準(zhǔn)面向全行業(yè)開(kāi)放,相關(guān)白皮書(shū)已提供下載,規(guī)范也可以聯(lián)系UCIe聯(lián)盟獲得。

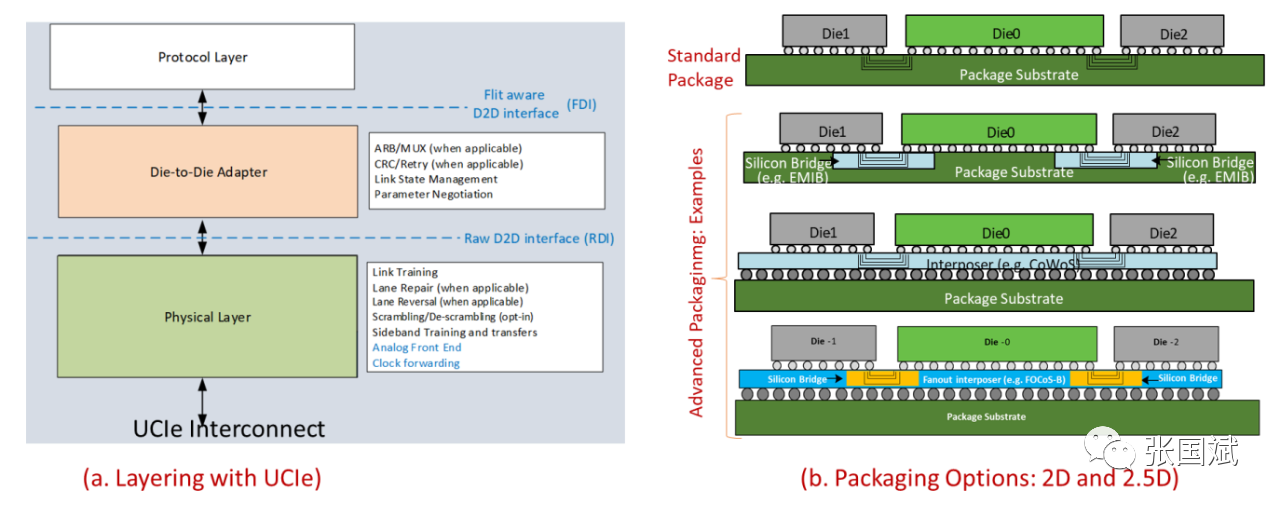

UCIe是一個(gè)分層協(xié)議,如上圖所示。物理層負(fù)責(zé)的是電信號(hào)、時(shí)鐘、鏈路訓(xùn)練、邊帶等。芯片到芯片的適配器提供了鏈接狀態(tài)管理和參數(shù)協(xié)商。它可以通過(guò)循環(huán)冗余保證數(shù)據(jù)的可靠傳輸。它可以通過(guò)循環(huán)冗余檢查(CRC)和鏈路級(jí)重試機(jī)制保證數(shù)據(jù)的可靠傳輸。當(dāng)支持多種協(xié)議時(shí)它定義了底層仲裁機(jī)制。一個(gè)256字節(jié)的FLIT(流控制單元)定義了底層傳輸機(jī)制,當(dāng)適配器負(fù)責(zé)可靠傳輸時(shí)。UCIe對(duì)PCIe和CXL協(xié)議進(jìn)行了原生映射,因?yàn)檫@些協(xié)議被廣泛部署在板級(jí),跨越計(jì)算的所有部分。這樣做是為了通過(guò)利用現(xiàn)有的生態(tài)系統(tǒng)來(lái)確保無(wú)縫的互操作性。

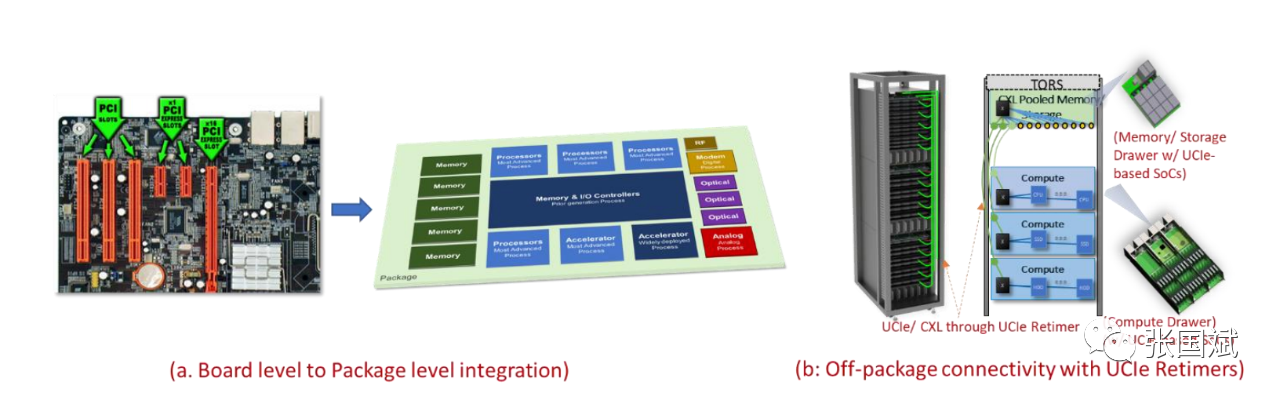

UCIe支持兩種廣泛的使用模式。第一種是封裝級(jí)集成,以提供高功率和高性價(jià)比的性能,如圖5a所示。連接在板級(jí)上的組件如內(nèi)存、加速器、網(wǎng)絡(luò)設(shè)備、調(diào)制解調(diào)器等,可以在封裝層面上進(jìn)行集成。適用于從手持設(shè)備到高端服務(wù)器,并通過(guò)不同的封裝方案將來(lái)自多個(gè)來(lái)源的芯片連接起來(lái)甚至在同一個(gè)封裝上通過(guò)不同的封裝選項(xiàng)連接。第二種用途是利用UCIe提供非包裝連接,使用不同類型的介質(zhì)(如光纜、電線、毫米波)。

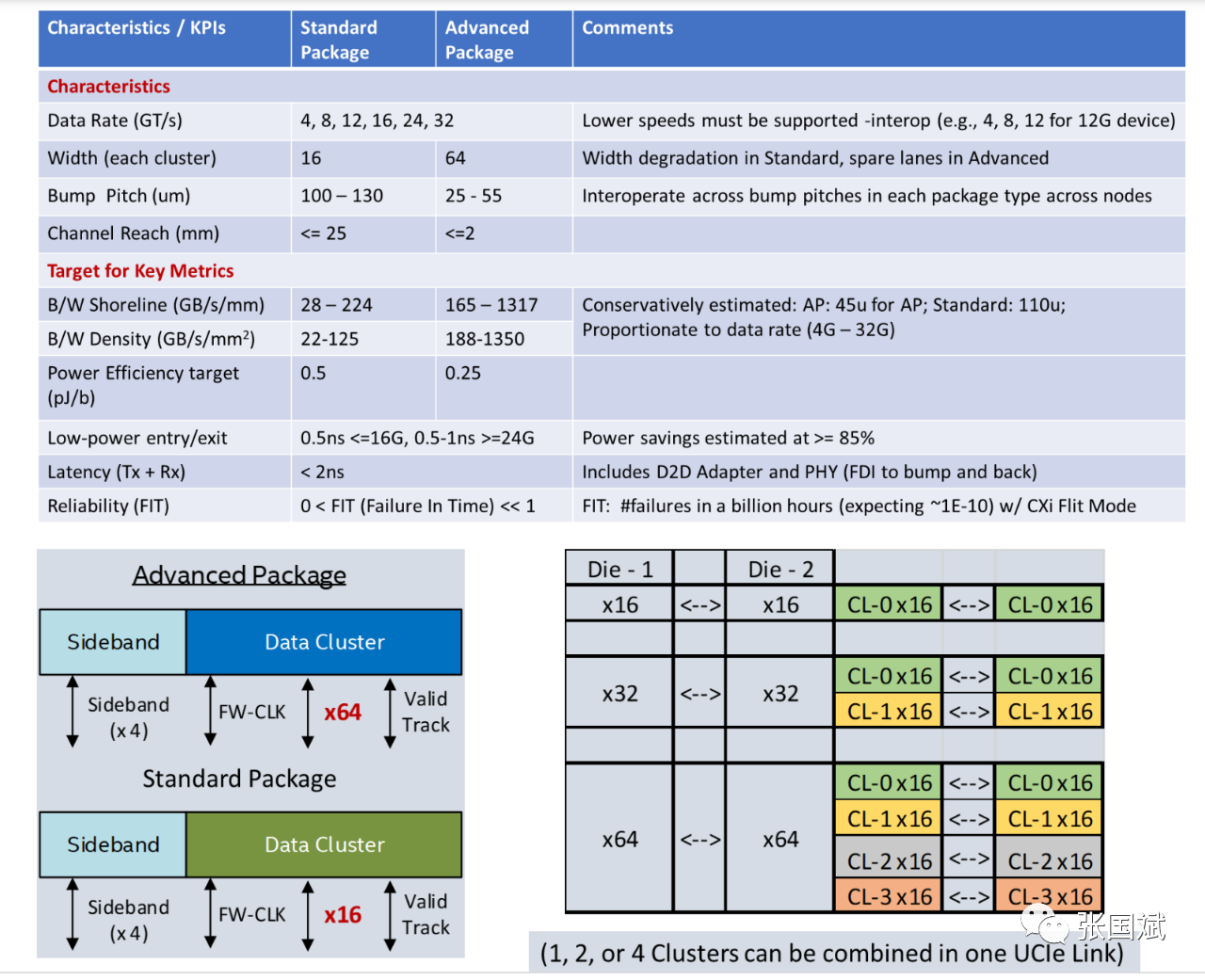

UCIe支持不同的數(shù)據(jù)速率、位寬、凸點(diǎn)間距和信道范圍,以確保最廣泛的互操作性。上表1中詳細(xì)列出了最廣泛的互操作性。它定義了一個(gè)邊帶接口,便于設(shè)計(jì)和驗(yàn)證。互聯(lián)的結(jié)構(gòu)單元是一個(gè)集群,包括N個(gè)單端、單向、全雙工的數(shù)據(jù)通道(標(biāo)準(zhǔn)封裝的N=16,高級(jí)封裝的N=64)。可以說(shuō),UCIe的發(fā)布打通了Chiplet未來(lái)發(fā)展障礙,對(duì)于推動(dòng)Chiplet有歷史性的意義。

| 相關(guān)新聞: |

| 另辟蹊徑再續(xù)摩爾定律 |

| 再次拯救摩爾定律:一文了然GAA芯片技術(shù) |

| 芯片上的突破 我國(guó)科學(xué)家制成世界上柵極長(zhǎng)度最小晶體管 |

學(xué)習(xí)園地