應(yīng)用材料公司是第一家在 2016 年推出下一代選擇性蝕刻系統(tǒng)(有時(shí)稱為高選擇性蝕刻)的供應(yīng)商。現(xiàn)在,Lam Research、TEL 和其他公司正在推出具有高選擇性蝕刻能力的工具,為未來的設(shè)備做準(zhǔn)備例如 3D DRAM 和環(huán)柵晶體管。

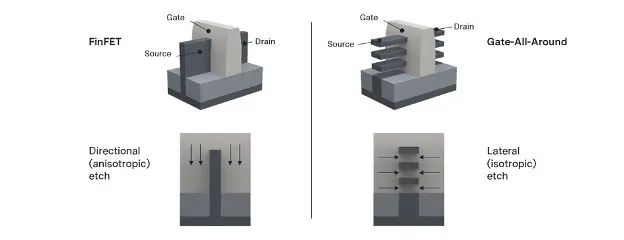

通過高選擇性蝕刻,專用蝕刻工具在 IC 生產(chǎn)過程中去除或蝕刻掉微小芯片結(jié)構(gòu)中的材料。此外,這些高選擇性蝕刻工具能夠在任何方向(各向同性)去除材料,而不會(huì)損壞器件的其他部分。在某些情況下,高選擇性蝕刻工具也可以在一個(gè)方向(各向異性)去除材料。今天,一些現(xiàn)有的蝕刻工具可以在一定程度上進(jìn)行選擇性蝕刻,但它們?cè)谶@方面的能力有限,無法在高級(jí)節(jié)點(diǎn)上創(chuàng)建新的器件結(jié)構(gòu)。

圖 1:從finFET到GAA 的過渡推動(dòng)了關(guān)鍵的各向同性選擇性蝕刻要求。資料來源:LAM Research

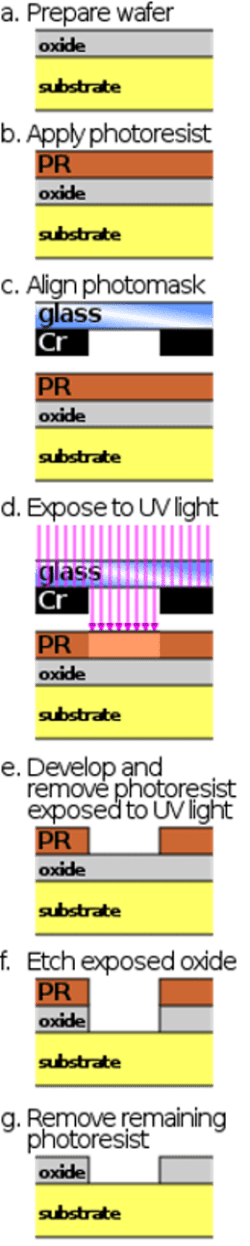

使用了幾十年,蝕刻是晶圓廠中必不可少的工藝。在一個(gè)簡(jiǎn)單的工藝流程中,系統(tǒng)將二氧化硅材料沉積在晶圓上。然后,光刻系統(tǒng)在晶圓上每個(gè)裸片的材料上形成微小特征圖案,蝕刻工具去除每個(gè)裸片上不需要的材料,以創(chuàng)建各種結(jié)構(gòu),以達(dá)到埃級(jí)精度 (1? = 0.1nm) 的目標(biāo)。

圖 2:晶圓廠中的一般圖案化和蝕刻工藝步驟。

資料來源:維基百科

基本上,先進(jìn)的蝕刻工具是一個(gè)帶有腔室的獨(dú)立系統(tǒng)。在操作中,將晶片插入腔室中。在一種類型的蝕刻中,等離子體(一種電離氣體)在腔室中產(chǎn)生。“首先,我們制造等離子體。電子撞擊氣體分子。這會(huì)產(chǎn)生離子和更多的電子。它們還會(huì)產(chǎn)生自由基。自由基成為在等離子體蝕刻系統(tǒng)中進(jìn)行化學(xué)蝕刻的物質(zhì)。這些自由基擴(kuò)散到晶片表面。它可能會(huì)與一種材料發(fā)生反應(yīng),但不會(huì)與另一種材料發(fā)生反應(yīng)。最后,你有一個(gè)蝕刻。結(jié)果是一個(gè)各向同性的過程。如果化學(xué)成分合適,它的選擇性就會(huì)非常高,”Fractilia 的首席技術(shù)官 Chris Mack 在視頻演示中解釋道。基本上,自由基是原子、分子或離子。

并非所有芯片工藝都需要高度選擇性的蝕刻。在芯片生產(chǎn)中,許多蝕刻步驟很簡(jiǎn)單,并且使用現(xiàn)有的蝕刻工具。對(duì)于要求更高的芯片工藝,蝕刻供應(yīng)商提供了涉及更復(fù)雜工具的各種選項(xiàng)。高選擇性蝕刻就是這樣一種選擇。使用專有化學(xué)物質(zhì),具有這些功能的蝕刻工具可以去除目標(biāo)材料,而無需修改或去除周圍層。

這個(gè)過程類似于原子層蝕刻 (ALE),但它們?cè)谠S多方面都不同。基本上,ALE 在原子尺度上選擇性地去除目標(biāo)材料。“在 ALE 中,你試圖一次移除一個(gè)原子層。TechInsights 的副主席Dan Hutcheson 說,您擁有極高的一致性,而且您不必移除整個(gè)薄膜。“通過選擇性蝕刻,您將在薄膜上敲打直到它完全消失。選擇性蝕刻的優(yōu)點(diǎn)是你可以走得更快。關(guān)鍵是你不能損壞它下面或周圍的東西。”

選擇性蝕刻還涉及其他因素。“根據(jù)定義,當(dāng)你蝕刻時(shí),選擇性是你想要去除的東西和你不想去除的東西之間的比率,”Hutcheson 說。

在一個(gè)示例中,芯片制造商將二氧化硅材料沉積在基板上。芯片制造商希望在設(shè)備中間保留該材料的選定部分,但希望移除其余部分。為此,將光刻膠掩模材料沉積在中間部分上。

在蝕刻過程中,腔室中的蝕刻劑(等離子體、氣體/蒸汽、酸)轟擊晶片。蝕刻物質(zhì)對(duì)掩模材料的反應(yīng)較慢,但與暴露的二氧化硅反應(yīng)較快并去除。

選擇性是指暴露材料與其底層或暴露材料與相鄰材料之間的反應(yīng)性差異。換句話說,根據(jù) Plasma-Therm 公司的設(shè)備制造商 Corial 的說法,選擇性是任何兩種材料之間蝕刻速率的比率。

“選擇性蝕刻是指以 >1000:1 的極高選擇性去除材料的過程,并且材料損失很小:<2? 或一個(gè)單層原子。綜上所述,正常的蝕刻選擇性在 20:1 范圍內(nèi),”Lam Research 產(chǎn)品營(yíng)銷總監(jiān) Ian Latchford 說。

盡管如此,越來越多的應(yīng)用需要高度選擇性的蝕刻。所有這些都需要具有復(fù)雜化學(xué)成分的專用且昂貴的選擇性蝕刻工具。

蝕刻模式

根據(jù) TechInsights 的數(shù)據(jù),總體而言,全球蝕刻市場(chǎng)從 2020 年的 140 億美元增長(zhǎng)到 2021 年的 199 億美元。據(jù)該公司稱,蝕刻市場(chǎng)預(yù)計(jì)在未來五年內(nèi)將以每年 7% 的速度增長(zhǎng)。AMEC、應(yīng)用材料、日立、Lam、Plasma-Therm 和 TEL 都是蝕刻業(yè)務(wù)的參與者。

在 IC 行業(yè)的早期,芯片制造商制造自己的設(shè)備。根據(jù)現(xiàn)在隸屬于 TechInsights 的 VLSI Research 的歷史資料,在過去,蝕刻工藝是在通風(fēng)櫥下的水槽中進(jìn)行的。基本上,晶圓被浸入充滿化學(xué)蝕刻劑的水槽中,然后沖洗。這去除了晶片上的材料。

在 1960 年代后期,現(xiàn)已倒閉的芯片制造商 Signetics 進(jìn)行了最早的等離子蝕刻工作。到 1970 年代,出現(xiàn)了幾家商業(yè)蝕刻設(shè)備供應(yīng)商。

早期,蝕刻技術(shù)演變成兩個(gè)部分——濕法蝕刻和干法蝕刻。在一個(gè)系統(tǒng)中,濕法蝕刻通過將晶片浸入液體溶液中來去除材料。

干法蝕刻是兩個(gè)市場(chǎng)中較大的一個(gè),廣泛用于當(dāng)今芯片的生產(chǎn)。干法蝕刻分為三個(gè)部分或模式——等離子蝕刻、反應(yīng)離子蝕刻 (RIE) 和濺射蝕刻(又名離子束蝕刻)。每種模式用于不同的應(yīng)用。

從技術(shù)上講,選擇性蝕刻是一種應(yīng)用,而不是一個(gè)單獨(dú)的類別。它適用于濕蝕刻和干蝕刻類別。在所有情況下,目標(biāo)都是在晶圓上進(jìn)行具有良好均勻性的精確蝕刻。

濺射或離子束蝕刻是一個(gè)物理過程。在操作中,將芯片插入系統(tǒng)中。該工具以加速的速度產(chǎn)生離子,從而去除芯片中的材料。

RIE 開發(fā)于 1970 年代,是一種等離子體工藝,廣泛用于當(dāng)今的芯片中。在操作中,離子在系統(tǒng)中產(chǎn)生,然后轟擊晶片的表面。這反過來又會(huì)去除芯片中的材料。

與此同時(shí),等離子蝕刻則不同。“在這個(gè)系統(tǒng)中,第一步是產(chǎn)生高密度等離子體,它由許多不同反應(yīng)性的電子、離子和中性物質(zhì)組成,”Imec 蝕刻研發(fā)工程師 Philippe Bézard 說。“然后,您可以使用離子過濾器(可視化一個(gè)帶有小孔的板)或?qū)A施加更大的氣體壓力來過濾掉離子,讓時(shí)間中和離子。”

剩余的自由基在晶片表面上擴(kuò)散,然后被吸收。“來自底物的原子和來自氣相的其他分子之間會(huì)發(fā)生反應(yīng),形成揮發(fā)性分子,”Bézard 說。

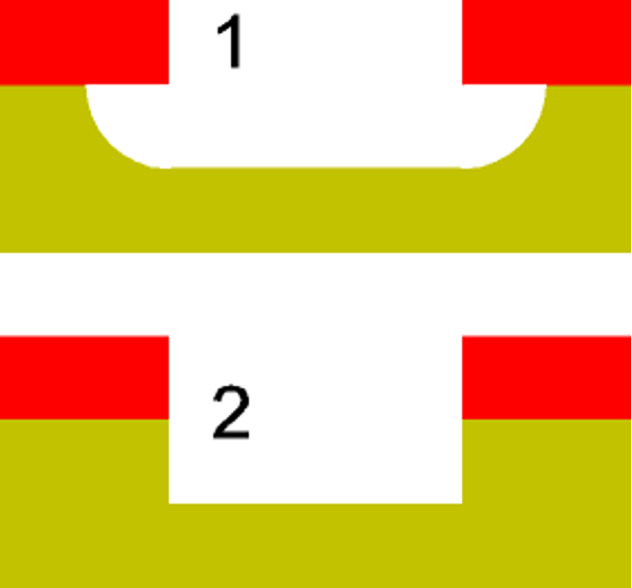

每種蝕刻模式都有不同的屬性,例如選擇性和方向性。方向性涉及各向異性和各向同性蝕刻。

“(在濺射蝕刻中),我們可以獲得高各向異性,但不能獲得高選擇性,”Fractilia 的 Mack 解釋說。“RIE 可以產(chǎn)生良好的選擇性、高各向異性和適中的蝕刻速率。控制有時(shí)很困難。”

有時(shí),芯片制造商需要更多的單向和選擇性蝕刻。這就是等離子體蝕刻的用武之地。“一般來說,這個(gè)過程是各向同性的,具有潛在的高選擇性,”Mack說。“為了獲得更高的選擇性,我們需要化學(xué)。”

圖 3:各向同性或多向蝕刻(頂部)與各向異性或定向蝕刻(底部) 來源:維基百科

ALE 與選擇性蝕刻

許多先進(jìn)芯片都需要高度選擇性蝕刻。多年來,半導(dǎo)體行業(yè)為存儲(chǔ)器和邏輯開發(fā)了新的復(fù)雜器件。

從 2011 年開始,一些代工供應(yīng)商開始提供使用最先進(jìn)的 finFET 晶體管的先進(jìn)工藝。IC 供應(yīng)商已經(jīng)圍繞 finFET 開發(fā)了芯片。如今,代工廠客戶正在出貨使用 16nm/14nm、7nm 和 5nm 工藝節(jié)點(diǎn)的 finFET 的芯片。3nm finFET 正在研發(fā)中。

此外,在 3nm 和/或 2nm,一些代工廠將遷移到環(huán)柵 (GAA),這是一種速度更快的晶體管,比 finFET 消耗更少的功率。但 GAA FET 也更昂貴且更難制造。

與此同時(shí),內(nèi)存制造商正在開發(fā)更先進(jìn)的 3D NAND、DRAM 和各種下一代內(nèi)存類型。

這些設(shè)備給設(shè)備制造商帶來了巨大的制造挑戰(zhàn),這正在影響更先進(jìn)的工藝和工具的開發(fā)。對(duì)于先進(jìn)的晶體管和最新的 DRAM,芯片制造商正在使用極紫外 (EUV) 光刻技術(shù),這是一種 13.5nm 波長(zhǎng)系統(tǒng),用于對(duì)芯片中的微小特征進(jìn)行圖案化。

沉積和蝕刻工具的供應(yīng)商也面臨著一些挑戰(zhàn)。“有很多過程挑戰(zhàn),”TEL 技術(shù)人員的高級(jí)成員羅伯特克拉克在最近的 IEDM 會(huì)議上發(fā)表演講時(shí)說。“每一代都會(huì)導(dǎo)致我們必須處理的長(zhǎng)寬比越來越高。這會(huì)產(chǎn)生各種蝕刻問題。你也有沉積問題。你的沉積物有保形、空隙和接縫。在蝕刻過程中會(huì)出現(xiàn)彎曲、彎曲、加載和選擇性問題。”

幸運(yùn)的是,蝕刻供應(yīng)商已經(jīng)開發(fā)出幾種新功能來應(yīng)對(duì)這些挑戰(zhàn)。ALE 和高選擇性蝕刻是其中的創(chuàng)新。

經(jīng)過多年的研發(fā),蝕刻供應(yīng)商在 2010 年代中期引入了 ALE 工藝。ALE 在原子尺度上選擇性地去除目標(biāo)材料。

在 ALE 的一個(gè)示例中,晶片位于 ALE 系統(tǒng)的腔室中。第一步是在腔室的硅表面上注入氯氣。氯分子被吸附在表面上,從而改變了表面。然后,將氬離子注入腔室,轟擊表面并去除改性層。

有兩種類型的 ALE——等離子和熱。正在生產(chǎn)中的等離子 ALE 可實(shí)現(xiàn)各向異性蝕刻。仍在生根的熱 ALE 使用熱反應(yīng)進(jìn)行各向同性蝕刻。

“等離子或熱 ALE 更多的是對(duì)蝕刻前沿的極端控制,而不是整體選擇性,”Imec 的 Bézard 說。“有時(shí)它比傳統(tǒng)的等離子蝕刻更好,有時(shí)它更糟。但選擇性遠(yuǎn)低于高選擇性蝕刻所需和實(shí)現(xiàn)的水平。”

此外,ALE 速度慢,各向同性能力有限。在某些情況下,ALE 可以對(duì)結(jié)構(gòu)造成最小的損害。

高選擇性蝕刻是不同的。“高選擇性蝕刻本身就是一種蝕刻方法。高選擇性蝕刻是一種技術(shù),可以實(shí)現(xiàn)選擇性是最重要規(guī)格的應(yīng)用,”Imec 的 Bézard 說。

多年來,選擇性蝕刻一直用于芯片生產(chǎn),但技術(shù)有限。“在引入早期選擇性蝕刻系統(tǒng)之前,想要進(jìn)行各向同性蝕刻的芯片制造商會(huì)使用濕法蝕刻,”Lam 的 Latchford 說。“但濕法蝕刻在精度、控制和材料方面極為有限,根本無法創(chuàng)造芯片制造商繼續(xù)向更小節(jié)點(diǎn)演進(jìn)所需的新器件結(jié)構(gòu)。”

隨著時(shí)間的推移,該行業(yè)開發(fā)了使用干法蝕刻的選擇性蝕刻工藝。今天,Applied、Lam、TEL 和其他公司提供具有下一代選擇性蝕刻功能的工具。供應(yīng)商對(duì)同一進(jìn)程使用不同的名稱。有人稱其為極端選擇性蝕刻、高度選擇性蝕刻或精密選擇性蝕刻。但它們都使用專用的腔室來實(shí)現(xiàn)使用專有化學(xué)物質(zhì)的高選擇性蝕刻。腔室安裝在標(biāo)準(zhǔn)蝕刻平臺(tái)上。

對(duì)于其選擇性蝕刻系統(tǒng),Applied 使用兩步方法來實(shí)現(xiàn)各向同性蝕刻。首先,對(duì)表面進(jìn)行處理。然后,產(chǎn)生自由基,從而去除目標(biāo)材料。

“基于自由基的方法提供了極高的選擇性。它可以蝕刻一種材料而不接觸另一個(gè)表面,”應(yīng)用材料公司副總裁 Uday Mitra 在 2017 年的一次采訪中解釋道。

與此同時(shí),Lam 最近推出了三種選擇性蝕刻產(chǎn)品——Argos、Prevos 和 Selis。Prevos 使用新穎的化學(xué)物質(zhì)為氧化物、硅和金屬提供選擇性蝕刻。Selis 采用自由基和熱蝕刻能力進(jìn)行選擇性蝕刻。Argos 選擇性地修改和凈化晶圓表面。

高選擇性蝕刻可用于存儲(chǔ)器和邏輯器件的各向異性或各向同性應(yīng)用。每個(gè)應(yīng)用程序也可以具有不同的選擇性。

“這完全取決于所使用的蝕刻應(yīng)用和類型,”Imec 的 Bézard 說,“對(duì)于等離子蝕刻,不同聚合物之間 50:1 的選擇性被認(rèn)為是非常高的。通常<10:1。例如,當(dāng)使用循環(huán)工藝(通常 >300:1)蝕刻硅對(duì)氧化物的選擇性時(shí),這將被認(rèn)為非常低。”

無論應(yīng)用程序如何,所有過程都具有挑戰(zhàn)性。“有一種通用蝕刻,它具有一定的選擇性。然后,當(dāng)您進(jìn)行選擇性蝕刻時(shí),您所談?wù)摰氖嵌鄠€(gè)數(shù)量級(jí)的更高選擇性,”TechInsights 的 Hutcheson 說。“當(dāng)你進(jìn)行純粹的選擇性蝕刻時(shí),它更接近于純粹的化學(xué)過程。但現(xiàn)在你必須弄清楚如何使化學(xué)作用發(fā)揮作用。您想過度蝕刻一點(diǎn),以確保清除所有材料。但是你不能走得太遠(yuǎn),否則你將開始移除底層材料。您越能提高選擇性,就越能確保在 300 毫米晶圓上進(jìn)行均勻蝕刻。我們談?wù)摰氖俏覀兲幚淼陌#臀覀儽仨毧缭?300 毫米水的精度而言。精度是驚人的。”

應(yīng)用

高選擇性蝕刻有多種應(yīng)用程序。例如,使用各向異性高選擇性蝕刻形成自對(duì)準(zhǔn)觸點(diǎn)。在芯片中,觸點(diǎn)是連接晶體管與器件中第一層銅互連的微小結(jié)構(gòu)。

同時(shí),在 2020 年,TEL 和 Imec 發(fā)表了一篇關(guān)于硅修整應(yīng)用的各向同性無等離子體工藝的論文。基本上,蝕刻工具修整薄膜或材料以形成所需的結(jié)構(gòu)形狀。該工藝可用于 finFET 和 GAA。

GAA 中使用了其他選擇性蝕刻工藝。在 3nm和/或 2nm工藝節(jié)點(diǎn),領(lǐng)先的代工廠及其客戶最終將遷移到稱為納米片 FET 的 GAA 晶體管類型。納米片 FET 是一種已旋轉(zhuǎn) 90 度的 finFET,從而形成水平堆疊的鰭,每個(gè)鰭之間具有垂直柵極材料。每個(gè)鰭片都像一張紙,是一個(gè)通道。

為了在晶圓廠中制造納米片,外延工具在基板上沉積超薄、交替的硅鍺 (SiGe) 和硅層,形成超晶格結(jié)構(gòu)。這種結(jié)構(gòu)可能具有三層、五層或更多層的每種材料。

微小的垂直鰭在超晶格結(jié)構(gòu)中被圖案化和蝕刻。然后,形成內(nèi)間隔物。為此,超晶格結(jié)構(gòu)中的SiGe層的外部被凹陷,然后用介電材料填充。

KLA 工藝控制解決方案總監(jiān) Andrew Cross 表示:“內(nèi)部間隔模塊提供了對(duì)有效柵極長(zhǎng)度的控制,并將柵極與源極/漏極外延隔離開來。” “在內(nèi)隔板形成的每個(gè)步驟中,精確控制壓痕和最終隔板凹槽的形狀和 CD 對(duì)于確保正確的器件性能至關(guān)重要。”

接下來,形成源極/漏極。然后,去除超晶格結(jié)構(gòu)中的 SiGe 層,留下構(gòu)成通道的硅基層或片。

Onto Innovation 戰(zhàn)略項(xiàng)目高級(jí)總監(jiān) Scott Hoover 說:“通道釋放需要單獨(dú)控制板材高度、角侵蝕和通道彎曲。”

最后,通過沉積高k電介質(zhì)和金屬柵極材料形成柵極。每個(gè)步驟都提出了一些挑戰(zhàn),特別是內(nèi)部間隔和通道釋放過程。

“對(duì)于納米片器件制造中的每個(gè)關(guān)鍵步驟,關(guān)鍵是采用高度選擇性的氣相蝕刻工藝,”IBM Research 的高級(jí)技術(shù)人員 Nicolas Loubet 說。“關(guān)于溝道釋放,需要 >150:1 的 SiGe 與 Si 蝕刻選擇性以防止納米片硅溝道損失,這可能導(dǎo)致遷移率下降、高溝道電阻和具有不同納米片寬度的器件之間的大可變性。蝕刻工藝還需要以受控的蝕刻速率完全蝕刻小腔中的 SiGe,并且不應(yīng)成為自限性。”

在最近的一篇論文中,IBM 和 TEL 展示了一種用于 GAA 的橫向干法蝕刻技術(shù),該技術(shù)使用新型化學(xué)物質(zhì),可實(shí)現(xiàn) >150:1 的選擇性。

與此同時(shí),Lam 還開發(fā)了一種用于 GAA 內(nèi)部間隔和釋放步驟的高選擇性蝕刻工藝。例如,對(duì)于通道凹槽步驟,Lam 結(jié)合了其新的 Prevos 和 Selos 工具。

“在 GAA 結(jié)構(gòu)中,僅去除了 SiGe 材料層,而器件的其他每一塊都相對(duì)保持不變。有了這種能力,芯片制造商可以雕刻出需要埃級(jí)精度的納米級(jí)特征,以避免在蝕刻過程中去除、修改或損壞其他關(guān)鍵材料層,”Lam 的 Latchford 說。

無論工具供應(yīng)商如何,這都是一個(gè)艱難的過程。“挑戰(zhàn)不在于找到化學(xué)物質(zhì),”Imec 的 Bézard 說。“對(duì)于每個(gè)納米片,它也獲得了完全相同的選擇性,因?yàn)榈撞康募{米片將比頂部的納米片看到更多的蝕刻氣體與基板的相互作用。所以你可以有非常局部的差異。這就是我們需要魔法的地方。我們需要確保每個(gè)納米片都能看到與其他納米片相同的東西。”

圖 4:Lam的 Selis-Prevos 系統(tǒng)在納米片 FET 和其他工藝中蝕刻 SiGe/Si 疊層。資料來源:Lam

未來器件

未來器件也需要高度選擇性蝕刻,例如互補(bǔ) FET (CFET),一種 3D 堆疊邏輯器件。CFET 目前處于研發(fā)階段。

內(nèi)存是另一個(gè)應(yīng)用程序。今天,內(nèi)存制造商正在推進(jìn) DRAM 擴(kuò)展的下一階段,但隨著技術(shù)接近其物理極限,他們面臨著一些挑戰(zhàn)。

作為回應(yīng),存儲(chǔ)器制造商正在開發(fā) 3D DRAM,它在許多方面類似于 3D NAND。3D DRAM 距離量產(chǎn)還有幾年的時(shí)間。“在 3D DRAM 中,重大的設(shè)計(jì)變化解決了平面設(shè)計(jì)中面臨的許多縮放問題,同時(shí),也產(chǎn)生了對(duì)橫向選擇性蝕刻的巨大需求,”Lam 的 Latchford 說。

結(jié)論

可以肯定的是,業(yè)界正在開發(fā)一系列未來的設(shè)備。芯片制造商需要在多個(gè)領(lǐng)域使用更先進(jìn)的工具,例如沉積、檢測(cè)、光刻和計(jì)量。

高選擇性蝕刻是工具組合的重要補(bǔ)充。“這些解決方案使芯片制造商能夠制造出功能越來越強(qiáng)大和復(fù)雜的芯片,這些芯片可以支持計(jì)算和性能密集型技術(shù),例如自動(dòng)駕駛汽車、先進(jìn)的數(shù)字醫(yī)療保健和即將到來的元宇宙,”Latchford 說。

| 相關(guān)新聞: |

| 新六邊形硅有望催生下一代電子與能源設(shè)備 |

| 新研究向下一代腦機(jī)接口系統(tǒng)邁出重要一步 |

| 下一代儲(chǔ)備池計(jì)算速度提高百萬倍 |

學(xué)習(xí)園地