近年來,二維半導(dǎo)體已成為解決高尺寸晶體管中通道控制問題的主要潛在解決方案。隨著器件的縮小,通道厚度應(yīng)按比例縮小。否則,柵極電容將不足以控制電流的流動(dòng)。不幸的是,陷阱和其他界面缺陷會(huì)降低載流子遷移率,并且在薄通道中更為重要。硅通道厚度的實(shí)際極限似乎約為 3nm。

斯坦福大學(xué)研究員 Aravindh Kumar 在一次采訪中解釋說,二維過渡金屬二硫化物 (TMD),如 MoS2和 WSe2,之所以有趣,是因?yàn)樗鼈儧]有平面外的懸空鍵。頂部和底部表面的相互作用是有限的,對(duì)載體行為幾乎沒有影響。特別是MoS2,易于合成且非常穩(wěn)定。

盡管如此,TMD 沉積通常需要非常高的溫度,遠(yuǎn)高于通常使用的底柵結(jié)構(gòu)的公差。例如,在imec,研究員 Yuanyuan Shi 及其同事使用 1000°C MOCVD 工藝進(jìn)行 MoS2沉積。出于這個(gè)原因,大多數(shù)關(guān)于 TMD 器件的研究要么使用從散裝材料剝離的薄片,要么使用在藍(lán)寶石或二氧化硅上生長(zhǎng)然后轉(zhuǎn)移的獨(dú)立層。

雖然層轉(zhuǎn)移方法允許器件研究與工藝開發(fā)并行進(jìn)行,但低溫硅兼容沉積工藝對(duì)于 TMD 器件的商業(yè)化至關(guān)重要。在 12 月的 IEEE 電子設(shè)備會(huì)議上報(bào)告的工作中,英特爾高級(jí)研究工程師 Kevin O'Brien 和他的同事使用預(yù)先圖案化的金屬氧化物晶種來創(chuàng)建 WS2生長(zhǎng)的成核位點(diǎn)。將金屬源直接放置在晶片上避免了使用固體金屬氧化物 CVD 源。受控成核限制了TMD 晶體的位置,因此限制了與它們相關(guān)的晶界。

獨(dú)立式 MoS2片材的質(zhì)量取決于沉積工藝和原始基板。例如,在 ACS Nano 中,蘇塞克斯大學(xué)的研究員 Manoj Tripathi 及其同事報(bào)告說,通過 CVD 在二氧化硅基底上生長(zhǎng)的MoS2處于張力狀態(tài),因?yàn)樗诶鋮s過程中比二氧化硅收縮得更多。儲(chǔ)存的張力防止了皺紋的形成,這是剝落的 MoS2中的常見問題。

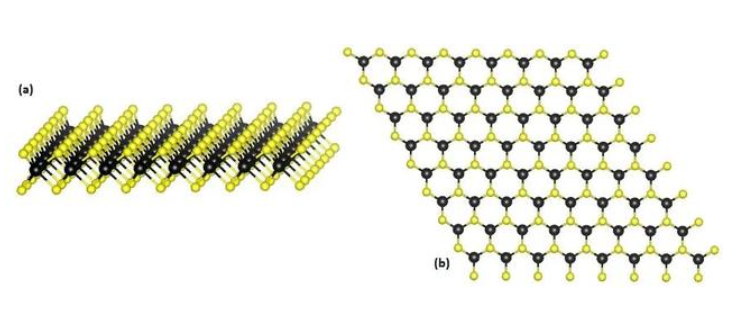

圖1:過渡金屬二硫?qū)倩飭螌拥木w結(jié)構(gòu):(a) 側(cè)視圖,(b) 俯視圖

優(yōu)化器件結(jié)構(gòu)

隨著薄膜的生長(zhǎng),進(jìn)入的分子自然會(huì)呈現(xiàn)出最有利的結(jié)構(gòu)。在 MoS2中,直接沉積在藍(lán)寶石上僅比沉積在預(yù)先存在的 MoS2表面上更有利。結(jié)果,具有多個(gè)MoS2層的島可以在與襯底接觸的層完成之前形成。這些島嶼的邊緣確實(shí)有懸空鍵,盡管使它們更具反應(yīng)性。Shi 的 imec 小組通過使用沉積后 Cl2蝕刻來優(yōu)先去除生長(zhǎng)島,從而利用邊緣反應(yīng)性。島的去除提高了在藍(lán)寶石上生長(zhǎng)的 MOCVD 薄膜的表面粗糙度和厚度均勻性。

正如硅器件的未來可能依賴于堆疊納米片一樣,TMD 晶體管可能需要多個(gè)堆疊通道來承載足夠的電流。北京大學(xué)教授熊雄及其同事通過轉(zhuǎn)移兩個(gè)大型獨(dú)立單分子層,然后將材料蝕刻到所需的器件尺寸,制造了堆疊的 MoS 在單個(gè)堆棧中使用 MoS2通道。相同的工藝也可用于制造堆疊互補(bǔ) FET,例如用于 NMOS 和 WSe2用于PMOS。

如上所述,目前最好的 MoS2器件取決于背柵設(shè)計(jì),其中柵極金屬和柵極氧化物沉積在硅襯底上,然后在頂部放置MoS2層。這種方法提供了更好的設(shè)備性能,但最終頂柵設(shè)備更具可擴(kuò)展性。與環(huán)柵硅晶體管一樣,具有匹配頂部和底部電容的雙柵將比單柵提供更好的通道控制。Imec 器件集成工程師 Xiangyu Wu 及其同事使用 GdAlOx中間層來改善雙柵極 MoS2器件中的電容匹配。中間層似乎可以減少短溝道效應(yīng)并改善閾值電壓控制。

制造獨(dú)立式 MoS2薄膜的工藝現(xiàn)在已經(jīng)足夠成熟,可以生產(chǎn)出統(tǒng)計(jì)上有用的設(shè)備數(shù)量。研究人員現(xiàn)在正在報(bào)告數(shù)千臺(tái)設(shè)備的統(tǒng)計(jì)數(shù)據(jù),這是可擴(kuò)展過程的先決條件。不幸的是,這數(shù)以千計(jì)的設(shè)備仍然落后于硅的性能基準(zhǔn)。與 TMD 的聯(lián)系尤其具有挑戰(zhàn)性。

進(jìn)行接觸

接觸電阻似乎有兩個(gè)來源。缺陷引起的間隙狀態(tài)來自于在 MoS2沉積期間或在金屬接觸形成期間產(chǎn)生的表面缺陷。臺(tái)積電的工作在沉積過程中使用氧氣來鈍化硫空位,這是缺陷的一種來源。Kumar 提出,來自熱激發(fā)接觸金屬的物理轟擊也有助于增加接觸電阻。斯坦福大學(xué)的工作使用了錫和銦,它們是低熔點(diǎn)材料,可以以最小的損壞進(jìn)行沉積。當(dāng)用金覆蓋時(shí),這些金屬形成在 450°C 以上穩(wěn)定的合金,使其與現(xiàn)有的 BEOL 工藝兼容。

金屬誘導(dǎo)的間隙狀態(tài)是接觸電阻的另一個(gè)貢獻(xiàn)者,導(dǎo)致費(fèi)米能級(jí)釘扎。當(dāng)費(fèi)米能級(jí)被釘扎時(shí),界面處的能壘高度與接觸金屬的功函數(shù)無關(guān),不能用于調(diào)節(jié)閾值電壓。半金屬作為潛在接觸很有趣,因?yàn)樗鼈冊(cè)谫M(fèi)米能級(jí)上沒有帶隙和低態(tài)密度。因此,它們往往不會(huì)產(chǎn)生 MIGS。在半金屬中,鉍和錫的熔點(diǎn)較低,分別為 271.5°C 和 231.9°C。銻的熔點(diǎn)為 630.6°C,更適合工藝。在 TSMC 提出的工作中,Ang-Sheng Chou 建議將 40% 或更多的銻與鉍合金化可以實(shí)現(xiàn)接觸勢(shì)壘高度、合金導(dǎo)電性和熔點(diǎn)的共同優(yōu)化。例如,

雖然英特爾集團(tuán)的最佳聯(lián)系人也使用銻,但他們警告說,MoS2 NMOS 器件遠(yuǎn)遠(yuǎn)落后于硅基準(zhǔn),在目標(biāo)亞閾值擺動(dòng)值下,電流比硅低 3 倍。對(duì)于WSe2 PMOS 器件,情況更糟。他們最好的器件使用釕觸點(diǎn),在 141 mV/decade 的亞閾值擺幅下實(shí)現(xiàn)了 50 μA/μm 的電流。

大多數(shù) 2D 半導(dǎo)體 FET 演示都使用頂部觸點(diǎn),因?yàn)樗鼈兏菀字圃臁2贿^,邊緣觸點(diǎn)更小,這可以減少整體器件的占用空間,也可以減少通道長(zhǎng)度的積極縮放。此外,如上所述,2D 材料的邊緣確實(shí)具有懸空鍵。與頂部觸點(diǎn)中存在的弱范德華鍵相比,邊緣觸點(diǎn)可能形成共價(jià)鍵。臺(tái)積電的 Terry Hung 在 2020 年 IEDM 上展示的工作表明,邊緣接觸消除了費(fèi)米能級(jí)釘扎。界面表面(二維材料邊緣的"中間線")形成一個(gè)偶極子,其效應(yīng)隨著距離的增加而迅速衰減。

結(jié)論

總體而言,二維半導(dǎo)體器件的前景充其量是喜憂參半。雖然最近的研究表明材料生長(zhǎng)和觸點(diǎn)制造方面取得了重大進(jìn)展,但尚未證明可以與前沿硅競(jìng)爭(zhēng)的設(shè)備。當(dāng)它們確實(shí)出現(xiàn)時(shí),它們很可能涉及與當(dāng)前晶圓廠不同的材料和工藝。

| 相關(guān)新聞: |

| 單原子厚二維磁鐵可在室溫下工作 |

| 量子氣體中首次實(shí)現(xiàn)二維超固體 |

| 二維材料首現(xiàn)奇異“多鐵性”狀態(tài) |

學(xué)習(xí)園地