但在最近的十年中,在競爭性營銷的推動(dòng)下,該標(biāo)簽已與實(shí)際最小柵極分離開來,并且可能比實(shí)際最小柵極長度小幾倍,同時(shí)也無法傳達(dá)該技術(shù)的其他基本特征。此外,來自不同半導(dǎo)體制造商的類似邏輯技術(shù)已經(jīng)貼上了不同的節(jié)點(diǎn)標(biāo)簽,從而造成了進(jìn)一步的混亂。

在開發(fā)中下一個(gè)節(jié)點(diǎn)(3 nm)的一位數(shù)納米標(biāo)簽只有大約十二個(gè)原子。這給人一種錯(cuò)誤的印象,即半導(dǎo)體技術(shù)將很快達(dá)到它無法克服的障礙。然而,已成定論的是,半導(dǎo)體產(chǎn)業(yè)將繼續(xù)取得進(jìn)步,這是因?yàn)槿杂性S多方法可以使半導(dǎo)體技術(shù)超越二維微型化,而且社會(huì)對功能更強(qiáng)大的電子系統(tǒng)的需求是無法滿足的。

因此,現(xiàn)在是半導(dǎo)體行業(yè)采用新指標(biāo)的時(shí)候了,該指標(biāo)正確地表明了半導(dǎo)體制造技術(shù)的進(jìn)步。通過使用這一新指標(biāo),行業(yè),研究機(jī)構(gòu),學(xué)術(shù)研究人員,學(xué)生,資助機(jī)構(gòu)和政府政策制定者可以識(shí)別和預(yù)測。

制定新指標(biāo)的理由

在被稱為摩爾定律的自我實(shí)現(xiàn)的預(yù)言的推動(dòng)下,半導(dǎo)體技術(shù)已取得了數(shù)十年的成倍發(fā)展。1965年,戈登·摩爾(Gordon Moore)觀察到,隨著新一代技術(shù)的發(fā)展,集成電路中晶體管的數(shù)量增加了一倍。自1971年以來,Intel 4004微處理器,晶體管的尺寸在芯片的二維平面上已經(jīng)縮小了大約1000倍,并且單個(gè)2-D芯片上的晶體管數(shù)量增加了約1500萬倍。而用來衡量集成密度這一驚人進(jìn)步的度量標(biāo)準(zhǔn)主要是芯片上晶體管的最小物理柵極長度。此物理尺寸(也稱為節(jié)點(diǎn))已被用作表征半導(dǎo)體制造技術(shù)的標(biāo)簽。

當(dāng)今,大批量生產(chǎn)中最先進(jìn)的技術(shù)被稱為7納米節(jié)點(diǎn),而5納米節(jié)點(diǎn)預(yù)計(jì)將在一年內(nèi)進(jìn)入大批量生產(chǎn)。因此,我們將很快用完納米來命名下一代技術(shù)。這給人一種錯(cuò)誤的印象,即半導(dǎo)體技術(shù)正在達(dá)到物理極限,將不再為信息技術(shù)和電子系統(tǒng)的未來發(fā)展做出貢獻(xiàn)。

的確,二維微型化最終將達(dá)到極限(原子的大小,并且可能早于此),并且有人認(rèn)為二維微型化的進(jìn)展已經(jīng)在放緩。同時(shí),也確實(shí)可以(而且將會(huì))通過許多其他手段獲得半導(dǎo)體技術(shù)的持續(xù)改進(jìn),這些手段已經(jīng)被研究(3-D集成是一個(gè)突出的例子)和尚未發(fā)明的新方法。

值得注意的是,自1990年代中期以來,代表技術(shù)發(fā)展的節(jié)點(diǎn)號已經(jīng)與用于識(shí)別技術(shù)的物理晶體管柵極長度脫鉤。自2000年代以來,“等效縮放比例” 的采用進(jìn)一步將技術(shù)的本質(zhì)與芯片內(nèi)部的物理尺寸脫鉤。

最近,設(shè)計(jì)技術(shù)協(xié)同優(yōu)化(DTCO)在每一代技術(shù)中都發(fā)揮了重要作用,并且基本上使節(jié)點(diǎn)號具有某種隨意性的名稱(類似于計(jì)算機(jī)的型號名稱),與技術(shù)的屬性無關(guān)。由于描述技術(shù)節(jié)點(diǎn)的標(biāo)簽與該節(jié)點(diǎn)的基本屬性脫節(jié),因此半導(dǎo)體行業(yè)及其研究和開發(fā)社區(qū)迫切需要一個(gè)簡單合理的度量標(biāo)準(zhǔn),以更好地表征日趨復(fù)雜和細(xì)微差別的下一代半導(dǎo)體技術(shù)。

邏輯,內(nèi)存,連接性(LMC)指標(biāo)

改進(jìn)的半導(dǎo)體器件密度直接轉(zhuǎn)化為更高級的計(jì)算系統(tǒng)的收益,而先進(jìn)的計(jì)算系統(tǒng)是推動(dòng)半導(dǎo)體技術(shù)進(jìn)步的主要?jiǎng)恿ΑR虼耍覀兘ㄗh使用以下三部分?jǐn)?shù)字作為衡量未來半導(dǎo)體技術(shù)進(jìn)步的指標(biāo):DL , DM , DC ,其中DL是邏輯晶體管的密度(以#/ mm 2為單位),DM是主存儲(chǔ)器的位密度(當(dāng)前為片外DRAM密度,以#/ mm 2為單位),DC是主內(nèi)存和邏輯之間的連接密度(以#/ mm 2為單位)。例如,文中發(fā)布的當(dāng)今最先進(jìn)的技術(shù)可以用[38M,383M,12K]來表征。作為另一個(gè)示例,多個(gè)邏輯和存儲(chǔ)管芯的3D堆疊可以增加DL , DM , 和DC。

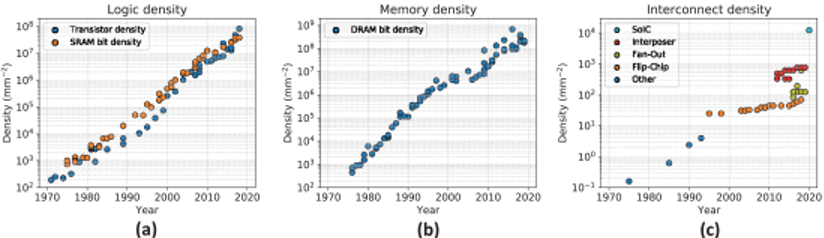

圖1:歷史邏輯密度 其中a、b、c分別是晶體管密度、Dram的位密度和存儲(chǔ)器和邏輯之間的互聯(lián)密度

圖1顯示了歷史邏輯,內(nèi)存和互連密度趨勢。在圖1(a)中,晶體管密度簡單地由晶體管的數(shù)量除以管芯面積來給出。然而,也已經(jīng)提出了更復(fù)雜的建議來計(jì)算晶體管密度,例如使用邏輯門密度的加權(quán)平均值(基于典型芯片設(shè)計(jì)中各種門的使用頻率)。圖1還顯示,每平方毫米的晶體管和SRAM位的數(shù)量一直在遵循非常相似的趨勢。

動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器(DRAM)位密度的歷史趨勢如圖1(b)所示。多年來的平均改善率可與DL改善。DRAM一直是計(jì)算系統(tǒng)的主要內(nèi)存,截至目前,它代表了DM系統(tǒng)指標(biāo)的組成部分。在使用替代存儲(chǔ)技術(shù)(例如新興的非易失性存儲(chǔ)器)的未來情況下,DM可以無縫地對應(yīng)于用作主存儲(chǔ)器的這種新存儲(chǔ)器的位密度。(片上)邏輯和(片外)主存儲(chǔ)器之間的互連密度可以視為邏輯到存儲(chǔ)器連接性的代表。

圖1(c)顯示了與各種封裝技術(shù)相關(guān)的片外互連的密度。這些密度值可以用作LMC指標(biāo)的組件DC 。但是,總的來說,DC不一定必須反映到片外存儲(chǔ)器的連接性。在主存儲(chǔ)器可以作為邏輯集成在芯片上的情況下,從系統(tǒng)的角度來看,邏輯和片上存儲(chǔ)器之間的連接可能變得非常重要,并且也可以表示為DC 。相比DL和 DM ,DC引入新技術(shù)后,其特點(diǎn)是有些離散的跳躍。在過去的十年中,通過對2.5D和3D封裝技術(shù)的實(shí)質(zhì)性改進(jìn),該存儲(chǔ)器在邏輯連接方面的發(fā)展獲得了顯著勢頭。

值得注意的是,DC是指主存儲(chǔ)器和邏輯電路之間的互連密度,無論這種連接是通過2.5D,3-D,單片3-D集成還是將來可能開發(fā)的其他技術(shù)進(jìn)行的。

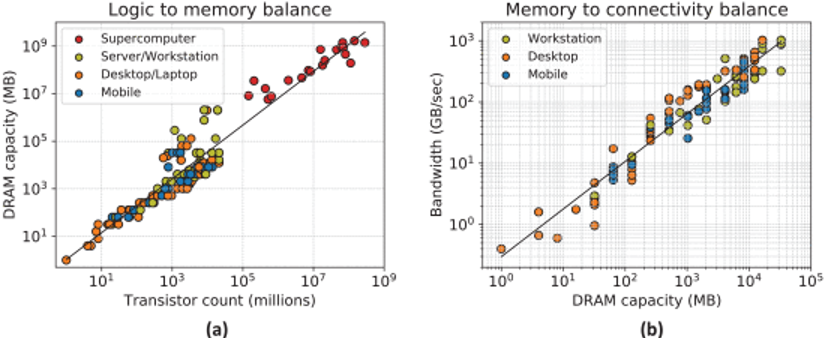

系統(tǒng)度量標(biāo)準(zhǔn)的這三個(gè)組成部分有助于計(jì)算系統(tǒng)的整體速度和能源效率。圖2中的歷史數(shù)據(jù)顯示邏輯,內(nèi)存和連接性的相關(guān)增長,這表明均衡的增長。在未來的幾十年中。DL , DM 和DC這種平衡在計(jì)算機(jī)體系結(jié)構(gòu)中是隱含的,并允許以最佳方式改善整體系統(tǒng)性能。圖2(a)顯示了從移動(dòng)/臺(tái)式處理器一直到世界上最快的超級計(jì)算機(jī),各種復(fù)雜程度的計(jì)算系統(tǒng)的DRAM容量與晶體管數(shù)量的關(guān)系。我們注意到,上述邏輯到存儲(chǔ)器的平衡在晶體管數(shù)量和主存儲(chǔ)器容量的八個(gè)數(shù)量級變化中保持不變,最佳擬合線對數(shù)據(jù)的斜率接近1。

圖2:計(jì)算系統(tǒng)中的資源平衡 其中圖a是DRAM容量與晶體管數(shù)量的比較,圖b是GPU的帶寬與DRAM容量的比較。

在主存儲(chǔ)器和邏輯之間提供足夠的連接性(帶寬)至關(guān)重要。否則,計(jì)算系統(tǒng)的速度和能源效率將受到內(nèi)存訪問的嚴(yán)重限制。在當(dāng)今的計(jì)算工作負(fù)載和系統(tǒng)中,這種內(nèi)存訪問挑戰(zhàn)已經(jīng)很明顯。盡管高帶寬存儲(chǔ)器(HBM)的成本相對較高,但仍被廣泛采用,這表明連通性至關(guān)重要。

實(shí)際上,圖2(b)中臺(tái)式機(jī)GPU的歷史帶寬與內(nèi)存容量的趨勢還表明,內(nèi)存容量和帶寬之間的平衡增長與邏輯和內(nèi)存之間的物理連接數(shù)(總線寬度)成正比。由于功率限制,時(shí)鐘頻率飽和,帶寬的提高可能越來越依賴于邏輯和存儲(chǔ)器之間連接的密度。根據(jù)系統(tǒng)設(shè)計(jì)和成本效益的折衷,邏輯和主存儲(chǔ)器之間的物理連接密度,DC的變化幅度大小不同:從印刷電路板到中介層,再到芯片到晶圓以及晶圓到晶圓的直接鍵合,最后到將來在單片3D集成芯片堆疊中的超密集層間過孔。

對半導(dǎo)體行業(yè)的好處

這個(gè)更全面的LMC密度指標(biāo)[DL , DM , DC ]可以用來捕獲半導(dǎo)體技術(shù)的基本技術(shù)屬性,這些技術(shù)正變得越來越復(fù)雜和細(xì)致。盡管公司可能會(huì)繼續(xù)使用其偏愛的標(biāo)簽來推銷其技術(shù),但是LMC密度度量可以用作衡量半導(dǎo)體制造商在其客戶和其他方之間技術(shù)進(jìn)步的一種通用語言,以促進(jìn)清晰的溝通。此度量標(biāo)準(zhǔn)考慮了將邏輯,內(nèi)存和連接集成到系統(tǒng)中所帶來的好處。除了與歷史趨勢和我們對計(jì)算系統(tǒng)的直覺保持一致之外,LMC密度度量標(biāo)準(zhǔn)還適用于并且可擴(kuò)展至未來的邏輯,存儲(chǔ)器和封裝/集成技術(shù)。

技術(shù)提供商和研究人員可以解決LMC指標(biāo)的一個(gè)或多個(gè)組成部分。提供最終產(chǎn)品(例如特定領(lǐng)域的硬件加速器)的公司可以選擇提及所有三個(gè)組件來描述特定的邏輯,內(nèi)存和封裝技術(shù),這些特定的邏輯,內(nèi)存和封裝技術(shù)被封存以構(gòu)建其產(chǎn)品的最新模型。這個(gè)三管齊下的指標(biāo)以全面的方式直接將設(shè)備技術(shù)的進(jìn)步與系統(tǒng)級的利益聯(lián)系起來,同時(shí)承認(rèn)各個(gè)組件之間的協(xié)同作用。

例如,具有3D封裝并堆疊多個(gè)邏輯和存儲(chǔ)管芯的半導(dǎo)體技術(shù)將相應(yīng)地增加DL 和DM ,因此,與采用相同邏輯和存儲(chǔ)技術(shù)但不具有3-D裸片堆疊功能的另一種可能的產(chǎn)品相比,該產(chǎn)品展示了這一進(jìn)步。

與技術(shù)公司類似,企業(yè),消費(fèi)者和政府機(jī)構(gòu)也可能發(fā)現(xiàn)這種對給定半導(dǎo)體技術(shù)狀態(tài)的更全面描述是有用和方便的。最重要的是,這種LMC密度度量的使用使半導(dǎo)體行業(yè)擺脫了使用消失的納米作為標(biāo)簽來描述半導(dǎo)體技術(shù)進(jìn)步的困惑,這種進(jìn)步對社會(huì)將在很長的時(shí)間內(nèi)保持非常重要的地位。

| 相關(guān)新聞: |

| 《超越摩爾定律的外延設(shè)備技術(shù)及市場趨勢2020》 |

| 科學(xué)家提出晶體管發(fā)展新思路 |

| 另辟蹊徑再續(xù)摩爾定律 |

學(xué)習(xí)園地