寫(xiě)入和讀取寄存器是控制和查詢大多數(shù)IP行為的主要方式。由于基本寄存器對(duì)設(shè)計(jì)的正確操作有直接影響,因此,寄存器測(cè)試是設(shè)計(jì)驗(yàn)證和啟動(dòng)時(shí)看似簡(jiǎn)單但很重要的一環(huán)。在IP級(jí)別,必須驗(yàn)證寄存器的正確實(shí)現(xiàn)——可以從IP塊上的接口訪問(wèn)它們。在子系統(tǒng)級(jí),驗(yàn)證對(duì)寄存器的訪問(wèn)有助于確認(rèn)已根據(jù)規(guī)范實(shí)現(xiàn)了互連網(wǎng)絡(luò)和地址解碼。在SoC級(jí)別,驗(yàn)證對(duì)寄存器的訪問(wèn)可以確認(rèn)處理器字節(jié)順序與互連實(shí)現(xiàn)是否匹配,并且引導(dǎo)代碼正確配置存儲(chǔ)器管理單元(MMU),使得IP寄存器對(duì)處理器可見(jiàn)。

在本文中,我們將探討通過(guò)Portable Stimulus Standard(PSS)的portable stimulus,如何利用寄存器模型中捕獲的信息來(lái)自動(dòng)創(chuàng)建塊、子系統(tǒng)和SoC寄存器訪問(wèn)測(cè)試。

UVM(Universal Verification Methodology,通用驗(yàn)證方法學(xué))提供了一個(gè)寄存器模型,用于對(duì)寄存器空間進(jìn)行建模 - 可用的寄存器、字段及其屬性,如地址、可訪問(wèn)性和復(fù)位值。UVM庫(kù)還提供內(nèi)置的定向序列,它們遍歷UVM寄存器模型并檢查寄存器的復(fù)位值,并通過(guò)修改和檢查所有讀/寫(xiě)寄存器字段來(lái)確認(rèn)寄存器是否可訪問(wèn)。這些內(nèi)置測(cè)試在IP級(jí)別非常有用,可以確認(rèn)單個(gè)IP塊內(nèi)的寄存器是否已正確實(shí)現(xiàn)。

然而,嘗試在子系統(tǒng)級(jí)重用這些測(cè)試序列變得很困難,因?yàn)樽酉到y(tǒng)中存在寄存器的數(shù)量以及內(nèi)置UVM序列是期望測(cè)試設(shè)計(jì)中的每個(gè)寄存器的定向序列的情況。嘗試在SoC級(jí)別重用這些內(nèi)置測(cè)試序列也很困難,因?yàn)閮?nèi)置序列是在SystemVerilog中實(shí)現(xiàn)的自檢序列。為了在SoC的嵌入式處理器上運(yùn)行,我們需要使用裸機(jī)C或匯編語(yǔ)言。

通過(guò)使用portable stimulus對(duì)測(cè)試意圖進(jìn)行建模,我們可以靈活地將測(cè)試空間劃分為多個(gè)較小的測(cè)試單元。我們還可以通過(guò)在C或匯編語(yǔ)言中創(chuàng)建嵌入式軟件測(cè)試來(lái)獲得針對(duì)SoC級(jí)別測(cè)試的靈活性。

portable stimulus可將測(cè)試中的兩個(gè)元素分開(kāi),這兩個(gè)元素通常在定向測(cè)試中合并。測(cè)試意圖是測(cè)試內(nèi)容的高級(jí)設(shè)計(jì),測(cè)試實(shí)現(xiàn)是執(zhí)行該測(cè)試的機(jī)制。

在測(cè)試寄存器模型的情況下,我們的測(cè)試意圖類似于以下內(nèi)容:

從寄存器塊中選擇一個(gè)寄存器

從寄存器中選擇讀/寫(xiě)字段

在該字段中選擇一個(gè)要測(cè)試的位

上述測(cè)試意圖與我們是否驗(yàn)證塊、子系統(tǒng)或SoC級(jí)設(shè)計(jì)無(wú)關(guān)。它也與SystemVerilog環(huán)境還是嵌入式軟件環(huán)境無(wú)關(guān)。

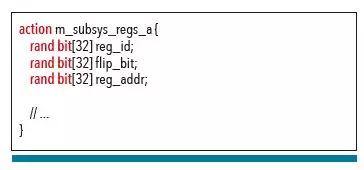

暫時(shí)忽略適當(dāng)?shù)募s束,我們測(cè)試單個(gè)寄存器的測(cè)試意圖由上面的PSS代碼捕獲:

有一個(gè)reg_id字段來(lái)捕獲我們正在測(cè)試的寄存器

有一個(gè)flip_bit字段來(lái)捕獲我們希望測(cè)試的寄存器中的哪個(gè)位

有一個(gè)reg_addr字段來(lái)捕獲內(nèi)存映射中字段的地址

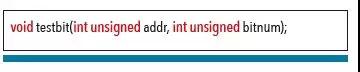

現(xiàn)在,如果沒(méi)有將此測(cè)試意圖連接到特定測(cè)試環(huán)境的測(cè)試實(shí)現(xiàn),我們的測(cè)試意圖就毫無(wú)價(jià)值。理想情況下,可以考慮用portable stimulus來(lái)設(shè)計(jì)我們的測(cè)試實(shí)現(xiàn)。這樣做可以讓我們?cè)O(shè)計(jì)一個(gè)可在所有環(huán)境中使用的通用API。例如,可以指定名為testbit的方法在所有環(huán)境中都可用,并且此方法將測(cè)試修改指定位的能力。這種功能的功能原型如下所示。

在SystemVerilog IP或子系統(tǒng)級(jí)環(huán)境中,我們可以將此方法實(shí)現(xiàn)為UVM序列中的任務(wù)。下面顯示的SystemVerilog任務(wù)使用內(nèi)存訪問(wèn)API來(lái)讀寫(xiě)內(nèi)存,并通過(guò)以下方式實(shí)現(xiàn)寄存器位測(cè)試操作:

讀取寄存器的當(dāng)前值

取消寄存器的目標(biāo)位,并寫(xiě)入新的寄存器值

讀回寄存器地址,并檢查該位是否保留其值

在上面顯示的示例中,如果遇到錯(cuò)誤,可以繼續(xù)運(yùn)行,這是UVM測(cè)試的典型特征。但是,嵌入式軟件環(huán)境具有不同的約束。

上面的示例顯示了嵌入式處理器的testbit函數(shù)的可能實(shí)現(xiàn)。如您所見(jiàn),該方法與SystemVerilog版本非常相似,但具體情況不同。最大的區(qū)別是:在這種情況下,假設(shè)如果寄存器位測(cè)試失敗,我們將結(jié)束整個(gè)測(cè)試。

分離測(cè)試意圖和測(cè)試實(shí)現(xiàn)是portable stimulus的核心要素,并且是使測(cè)試意圖在各種環(huán)境中輕松重新定位的關(guān)鍵。

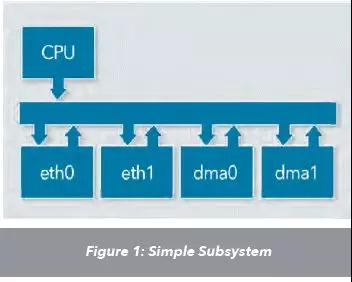

我們已經(jīng)研究了使用PSS捕獲測(cè)試意圖和測(cè)試實(shí)現(xiàn),以進(jìn)行寄存器測(cè)試的方法,下面簡(jiǎn)單地看看我們的UVM寄存器模型是如何形成的。出于本示例的目的,看一下圖1中非常簡(jiǎn)單的子系統(tǒng),該子系統(tǒng)有一個(gè)處理器、兩個(gè)以太網(wǎng)控制器和兩個(gè)DMA引擎。

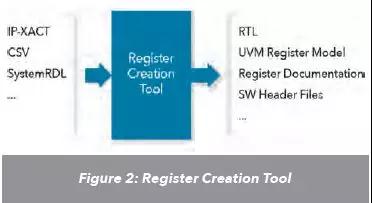

在塊級(jí)別驗(yàn)證以太網(wǎng)和DMA控制器時(shí),為其創(chuàng)建了UVM寄存器模型。這些UVM寄存器模型可以手工創(chuàng)建,但更有可能是使用寄存器創(chuàng)建工具創(chuàng)建的,如圖2所示。

寄存器創(chuàng)建工具接受各種標(biāo)準(zhǔn)(IP-XACT,SystemRDL)和非標(biāo)準(zhǔn)(例如,CSV)格式的寄存器規(guī)范,并可生成該寄存器規(guī)范的各種視圖。生成寄存器模型的RTL實(shí)現(xiàn)可節(jié)省設(shè)計(jì)實(shí)現(xiàn)的時(shí)間,生成UVM寄存器模型可縮短啟動(dòng)測(cè)試平臺(tái)的時(shí)間。在所有情況下,確保一切都與高級(jí)寄存器規(guī)范保持一致可以節(jié)省大量時(shí)間。

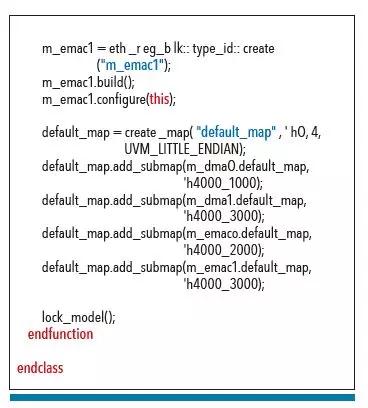

當(dāng)達(dá)到子系統(tǒng)級(jí)別時(shí),寄存器創(chuàng)建工具可以幫助我們?yōu)檎麄€(gè)子系統(tǒng)組裝寄存器模型。或者,我們可以簡(jiǎn)單地采用單獨(dú)的塊級(jí)寄存器模型并組裝子系統(tǒng)級(jí)寄存器模型。下面的代碼匯集了以太網(wǎng)和DMA控制器寄存器模型中的子系統(tǒng)級(jí)寄存器模型。如您所見(jiàn),不需要太多代碼。

設(shè)計(jì)中可用的寄存器及其地址

這些寄存器中的字段和任何訪問(wèn)限制

令人驚訝的是寄存器的數(shù)量累積的速度很快,當(dāng)我們?yōu)閮蓚€(gè)以太網(wǎng)控制器和兩個(gè)DMA控制器創(chuàng)建寄存器模型時(shí),有989個(gè)帶可測(cè)試字段的寄存器。試想一下完整的SoC包含多少寄存器!

現(xiàn)在我們已經(jīng)捕獲了子系統(tǒng)或SoC級(jí)寄存器模型,如何繼續(xù)創(chuàng)建寄存器訪問(wèn)測(cè)試呢?首先,需要?jiǎng)?chuàng)建寄存器訪問(wèn)測(cè)試意圖的PSS模型。然后,我們需要將測(cè)試意圖連接到具有測(cè)試實(shí)現(xiàn)的特定驗(yàn)證環(huán)境。

以前,我們查看了寄存器訪問(wèn)測(cè)試的核心測(cè)試意圖:選擇一個(gè)寄存器,并在該寄存器中進(jìn)行測(cè)試。當(dāng)然,這種高級(jí)測(cè)試意圖必須基于正在測(cè)試的設(shè)計(jì)中的寄存器來(lái)約束。好消息是我們已經(jīng)捕獲了在寄存器模型中生成這些約束所需的所有信息。

在某些情況下,我們的寄存器創(chuàng)建工具可能能夠直接創(chuàng)建PSS寄存器測(cè)試作為其輸出之一。如果沒(méi)有,那么自動(dòng)創(chuàng)建測(cè)試意圖的一種方法是:運(yùn)行SystemVerilog代碼,該代碼遍歷UVM寄存器模型并寫(xiě)出我們的PSS寄存器測(cè)試意圖。下面的代碼顯示了一個(gè)UVM測(cè)試,它調(diào)用名為regmodel2pss的類來(lái)創(chuàng)建PSS測(cè)試意圖。

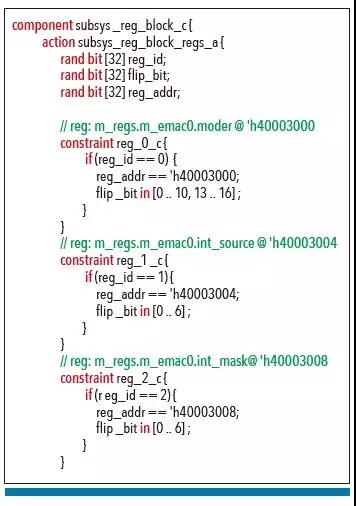

其結(jié)果是形成了一個(gè)portable stimulus描述,即捕獲我們的子系統(tǒng)寄存器映射的寄存器測(cè)試意圖。下面顯示的代碼是PSS組件的第一部分和為測(cè)試寄存器模型而創(chuàng)建的操作。

我們的操作(其名稱來(lái)自寄存器塊名稱)聲明了三個(gè)rand字段:reg_id字段包含目標(biāo)寄存器的ID,范圍介于0和寄存器數(shù)減1之間;flip_bit字段指定要測(cè)試的寄存器位,該字段以及寄存器地址將根據(jù)寄存器ID進(jìn)行約束。

上面自動(dòng)創(chuàng)建的約束將確保我們的操作根據(jù)被測(cè)試的寄存器產(chǎn)生有效的寄存器地址和flip_bit。

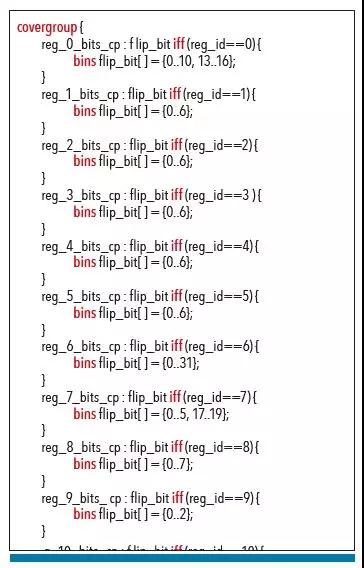

除了自動(dòng)創(chuàng)建約束外,還可以自動(dòng)創(chuàng)建PSS覆蓋模型,以確保已覆蓋寄存器中的所有寄存器和所有位。

一旦擁有核心寄存器測(cè)試意圖,我們需要將其集成到頂級(jí)PSS場(chǎng)景中。雖然核心寄存器測(cè)試意圖是從寄存器模型自動(dòng)派生的,但我們的頂級(jí)寄存器測(cè)試場(chǎng)景卻是手工創(chuàng)建的。

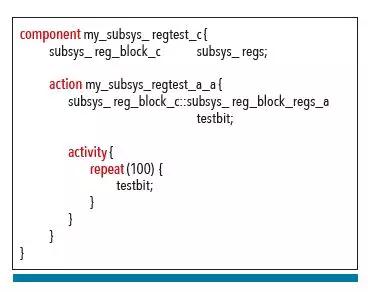

上圖顯示了測(cè)試場(chǎng)景,它構(gòu)建在編碼測(cè)試意圖的核心操作之上。根據(jù)PSS的要求,測(cè)試場(chǎng)景封裝在頂層組件中。我們?cè)陧敿?jí)組件中創(chuàng)建了一個(gè)register-test組件(subsys_reg_block_c)的實(shí)例,因?yàn)槲覀儗⑹褂迷摻M件中的操作。在頂級(jí)操作(my_subsys_regtest_a)中,創(chuàng)建了一個(gè)名為testbit的subsys_reg_block_regs_a操作實(shí)例,此操作內(nèi)部是register-test字段和covergroup的實(shí)例。在頂級(jí)操作中,運(yùn)行100次testbit,這意味著每次測(cè)試運(yùn)行時(shí),將測(cè)試100個(gè)寄存器位。

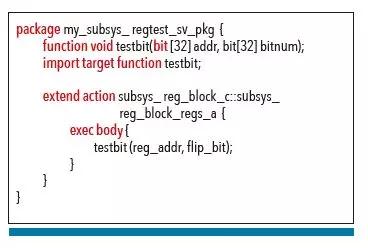

頂級(jí)測(cè)試場(chǎng)景實(shí)際上并沒(méi)有做任何事情,因?yàn)槿鄙贉y(cè)試實(shí)現(xiàn)。幸運(yùn)的是,PSS允許我們輕松地在測(cè)試實(shí)現(xiàn)中進(jìn)行分層,而無(wú)需更改核心描述 - 在本例中為subsys_reg_block_regs_a操作。

上圖顯示了利用PSS程序接口的SystemVerilog測(cè)試實(shí)現(xiàn)描述。聲明外部函數(shù)的簽名,并從操作的exec塊調(diào)用該函數(shù)。這種測(cè)試實(shí)現(xiàn)方式適用于所有支持可調(diào)用過(guò)程的環(huán)境,如C,C ++,SystemVerilog等。

在多數(shù)情況下,對(duì)SoC的裸機(jī)嵌入式軟件測(cè)試將用C語(yǔ)言編寫(xiě)。但是,如果需要?jiǎng)?chuàng)建匯編語(yǔ)言測(cè)試呢?幸運(yùn)的是,PSS也提供了相應(yīng)的方法!

在上面討論的測(cè)試實(shí)現(xiàn)中,我們使用PSS 目標(biāo)模板 exec塊來(lái)指定必須生成的匯編代碼片段(在這種情況下為RISC-V)以測(cè)試寄存器位。大括號(hào)(例如,{{reg_addr}})用于引用PSS模型中字段的當(dāng)前值,并將該值替換為生成的代碼。用匯編語(yǔ)言進(jìn)行測(cè)試實(shí)現(xiàn)肯定有它的局限性,但是當(dāng)需要特定技術(shù)時(shí),PSS就有可能實(shí)現(xiàn)。

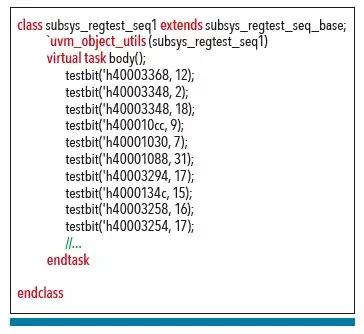

既然有測(cè)試意圖和測(cè)試實(shí)現(xiàn)來(lái)測(cè)試對(duì)寄存器的訪問(wèn),我們就可以開(kāi)始運(yùn)行測(cè)試了。在UVM環(huán)境中,PSS為我們提供了預(yù)生成定向測(cè)試或運(yùn)行PSS求解器引擎,以及模擬的靈活性。這兩種方法都有其優(yōu)點(diǎn)和缺點(diǎn)。一方面,定向測(cè)試很容易理解。

例如,上面的UVM序列非常容易理解,并且總是完全相同。但是,我們希望測(cè)試能夠在運(yùn)行不同的“種子”時(shí)略微不同。而且,我們希望能夠在回歸中運(yùn)行的不同模擬中輕松劃分成千上萬(wàn)的寄存器測(cè)試。這就是使用與模擬一起運(yùn)行的PSS求解器引擎真正有用的地方。使用不同種子運(yùn)行相同的序列會(huì)導(dǎo)致不同的行為,而像Questa?inFact這樣的PSS工具提供了專用功能,可以在回歸中運(yùn)行的模擬中動(dòng)態(tài)分區(qū)測(cè)試。

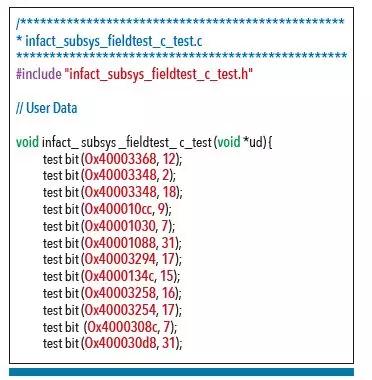

如果能夠在裸機(jī)軟件環(huán)境中使用C,我們就可以使用testbit函數(shù)實(shí)現(xiàn)和PSS程序接口來(lái)生成C測(cè)試代碼,如上所示。

但是,如果需要使用程序集,我們可以使用target-template exec塊測(cè)試實(shí)現(xiàn)來(lái)生成完全獨(dú)立的測(cè)試。該測(cè)試的片段測(cè)試了兩個(gè)寄存器/位組合。

寄存器測(cè)試是從IP到子系統(tǒng),再到SoC級(jí)別的所有環(huán)境中非常有用的“煙霧”測(cè)試。雖然UVM庫(kù)中的內(nèi)置寄存器測(cè)試序列主要用于IP級(jí)別,但在PSS模型中捕獲寄存器測(cè)試意圖使得寄存器測(cè)試功能可從IP移植到SoC級(jí)別,并且在控制哪些寄存器方面提供更大的靈活性。

寄存器生成工具的輸入文件和生成的UVM寄存器模型都包含足夠的信息來(lái)自動(dòng)創(chuàng)建portable stimulus測(cè)試意圖。這使得寄存器生成工具很容易添加對(duì)portable stimulus測(cè)試的支持。它還可以很容易地從現(xiàn)有UVM寄存器模型中獲取portable stimulus測(cè)試,無(wú)論它們是如何創(chuàng)建的。

因此,portable stimulus不僅適用于最難的測(cè)試,它還可以像看似簡(jiǎn)單的測(cè)試任務(wù)一樣輕松高效地應(yīng)用,例如注冊(cè)訪問(wèn)測(cè)試,它可以提供可移植性,從而減少重復(fù)工作。

學(xué)習(xí)園地