摘要:本文主要解釋了物理設(shè)計(jì)流程中遇到的各種DRC(設(shè)計(jì)規(guī)則檢查),討論了通常在block級(jí)看到的金屬DRC違規(guī)(7nm制程),并概述了解決它們的實(shí)用方法。

大多數(shù)VLSI工程師都了解DRC,并且非常了解DRC清理數(shù)據(jù)庫(kù)的必要性。本文將簡(jiǎn)要介紹不同類型的DRC違規(guī),它們?cè)谖锢碓O(shè)計(jì)中出現(xiàn)的原因以及修復(fù)它的啟發(fā)式方法。我們還將查看晶圓代工廠提出的DRC(例如:臺(tái)積電,英特爾,三星等),并探討它們?nèi)绾吾槍?duì)特定制程節(jié)點(diǎn)(例如28nm,16nm,7nm)進(jìn)行操作。

DRC(設(shè)計(jì)規(guī)則檢查)的主要目標(biāo)是在設(shè)計(jì)中實(shí)現(xiàn)可靠性并提高芯片的良率。晶圓代工廠提供的所有規(guī)則都以驗(yàn)證規(guī)則文件(物理驗(yàn)證工具的規(guī)則卡片文件)的形式作為物理驗(yàn)證工具的輸入提供。如果違反任何一項(xiàng)規(guī)則,DRC將會(huì)反映在設(shè)計(jì)中。

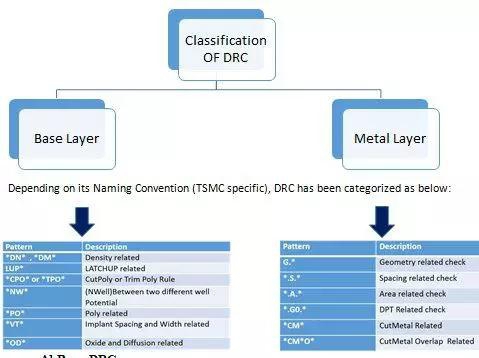

DRC的分類

DRC大致分為基礎(chǔ)層DRC和金屬層DRC,具體如下圖所示。

與FEOL(前端線)制程相關(guān)的DRC包括Nwell,N +,P +注入層,多晶硅,氧化物擴(kuò)散等被稱為基礎(chǔ)層DRC。這些DRC的修復(fù)工作需要改變FEOL層。物理設(shè)計(jì)人員遵循的一般做法是在布局規(guī)劃凍結(jié)之前或設(shè)計(jì)周期的簽核階段之前修復(fù)這些違規(guī)行為。

隨著時(shí)間的推移,技術(shù)的更新,APR流程被開(kāi)發(fā)為以增強(qiáng)的方式解決基礎(chǔ)DRC,以避免物理設(shè)計(jì)流程的后續(xù)PnR /簽核階段的故障。一些DRC可以根據(jù)不同代工廠遵循的DFM(可制造性設(shè)計(jì))實(shí)踐而變化。

基礎(chǔ)層違規(guī)的原因包括:

1.缺少Endcap / WellTap / Decaps / Filler單元格

2.填料放置不正確

3.填料添加不正確

4.重疊或特定內(nèi)存縮減模型的內(nèi)部結(jié)構(gòu)中的問(wèn)題(硬宏/ IP)

5.內(nèi)存不在網(wǎng)格上

6.定位問(wèn)題

7.輸入門完整性問(wèn)題

8.合法化問(wèn)題

9.不滿足兩個(gè)存儲(chǔ)器之間的鄰接要求(存儲(chǔ)器間隔規(guī)則根據(jù)技術(shù)和代工廠而變化)

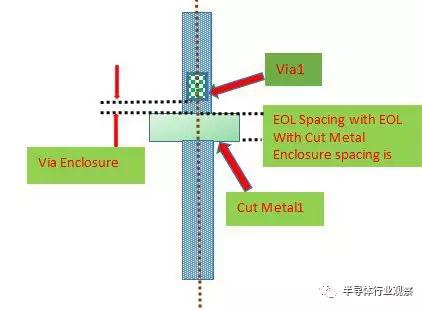

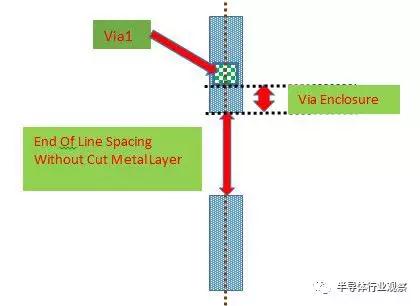

與BEOL(后端線)制程相關(guān)聯(lián)的DRC是包括用FEOL和外部設(shè)備插入的互連或金屬層的DRC。Cut Metal / Trim Metal DRC是7nm制程節(jié)點(diǎn)新推出的。Cut Metal是新層,它是為了最小化EOL(行尾)間距、MAR(Min Area)違規(guī)和Via Enclosure規(guī)則而引入的。

Cut Metal層的優(yōu)勢(shì):

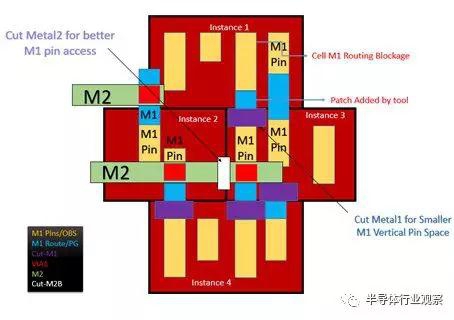

1.有助于保持較短的標(biāo)準(zhǔn)單元高度(CM1A和CM1B)[參見(jiàn)圖c以便更好地理解]。

2.由于CM2的存在,它有助于減少兩個(gè)標(biāo)準(zhǔn)單元之間的距離(左和右)[參見(jiàn)圖c以便更好地理解]。

3.更多M1路由資源可用性

4.Cut Metal層有助于解決EOL(縮小端到端間距),MAR和Enclosure違規(guī)[參見(jiàn)圖a和圖b]。

圖a:由于光刻約束,在該示例中,線端和通孔外殼間距更大

圖b:由于引入了Cut Metal層,線間距和通孔外殼間距明顯減小了

圖c:由于使用了Cut Metal1,實(shí)現(xiàn)了較短的標(biāo)準(zhǔn)單元高度,并且由于使用了Cut Metal2,因此可以實(shí)現(xiàn)單元聚集。

7nm金屬層DRC違規(guī)的一些真實(shí)場(chǎng)景

在這里,我們討論一下用于修復(fù)7nm ASIC設(shè)計(jì)中出現(xiàn)的DRC違規(guī)的技術(shù)。

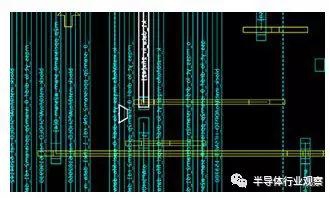

圖A.1:使用CM1A DRC

這里,梯形標(biāo)記表示在垂直金屬層(M1)處提示的錯(cuò)誤。該誤差是由于金屬軌道與兩個(gè)過(guò)孔之間存在的Cut Metal之間沒(méi)有最小間距(VIA12)。

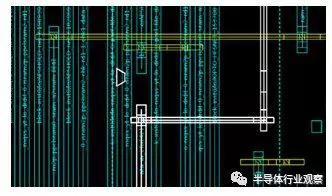

圖A.2:CM1A DRC修復(fù)

為了解決這個(gè)問(wèn)題,我們簡(jiǎn)單地將通孔(VIA12)從其初始位置向下移動(dòng)。如上圖所示,突出顯示的軌跡是新的布線,從藍(lán)色的垂直金屬層一(M1)到黃色的水平金屬層二(M2)。

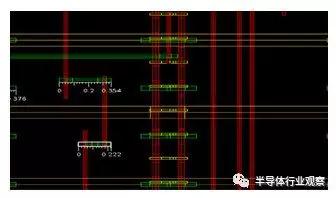

圖B.1:使用M4.A.1 DRC

該DRC簡(jiǎn)單地描繪了以綠色顯示的水平金屬軌道4(M4)的最小面積,其小于0.015平方微米。

圖B.2:用M4.A.1 DRC修復(fù)

為了解決這個(gè)問(wèn)題,我們擴(kuò)展了水平金屬層四(M4)軌道。如圖所示,重新布線的軌跡取自紅色的垂直金屬層3 (M3)和綠色的水平金屬層4(M4)。

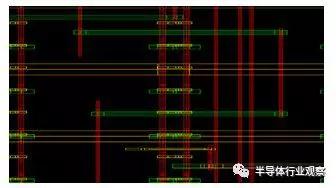

圖C.1:使用VIA2.S.20 DRC

在這里,由于黃色水平信號(hào)金屬軌道層2(M2)的通孔與同一層中的電源軌道的通孔之間的最小間距違規(guī),則DRC彈出。在該圖中,中心標(biāo)記是信號(hào)軌道,并且在三角形的拐角處,存在兩個(gè)電源軌道通孔。

圖C.2:用VIA2.S.20 DRC修復(fù)

通過(guò)將軌道重新布線遠(yuǎn)離電源過(guò)孔來(lái)解決該DRC問(wèn)題。如圖所示,帶有Z字形路由的突出顯示的軌道代表了消除此DRC的一個(gè)可能解決方案。

圖D.1:使用M3.CS.1.1.6:CA DRC

紅色的Cut Metal垂直層3(M3)違反了與藍(lán)色所示的存儲(chǔ)器IP的內(nèi)層的間隔的最小值規(guī)則。

圖D.2:使用M3.CS.1.1.6:CA DRC已修復(fù)

為了解決這種類型的問(wèn)題,我們將垂直金屬層三(M3)重新布線穿過(guò)黃色的水平金屬層二(M2)。

M1 Enclosure DRC可以在Calibre中以名稱H240 * M1.EN *彈出。它顯示M1 VIA內(nèi)部到單元引腳的DRC。這是由于添加的補(bǔ)丁測(cè)量值為0.028u,小于限值(<= 0.037u)。

為了修復(fù)DRC,我們可以將補(bǔ)丁擴(kuò)展到超過(guò)0.037u的限制。

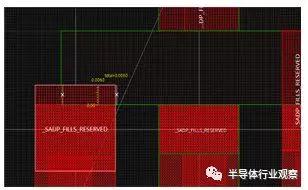

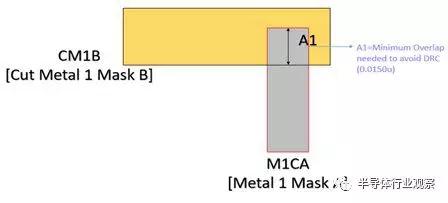

Cut Metal重疊DRC標(biāo)稱為CM1B.O. *。這是由于Mask 2的CutMetalM1或(Mask B)與Mask 1的M1或(Mask A)的重疊造成的。

在這種情況下,M1(MaskA)和CM1(MaskB)之間的垂直重疊是0.008u。只需讓補(bǔ)丁長(zhǎng)度> = 0.0150u,就可以修復(fù)DRC。

有關(guān)詳細(xì)信息,請(qǐng)參見(jiàn)下圖:

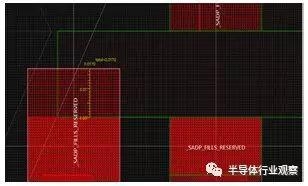

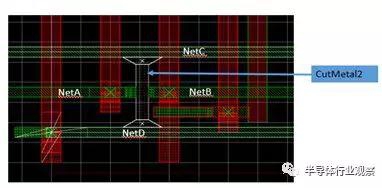

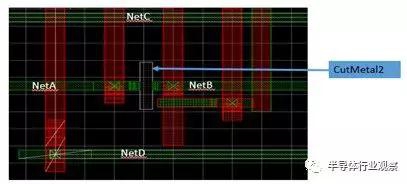

此DRC以名稱CM2 * S *彈出。

如上圖所示,Mask 2層M2的Cut Metal存在于兩個(gè)網(wǎng)之間:netA和netB。

Cut Metal2使用Metal2的NetC和NetD進(jìn)行間距違規(guī)。

通過(guò)重新路由NetC和NetD的一小部分,可以解決 Cut Metal間距DRC問(wèn)題。

結(jié)論

成功的ASIC芯片流片需要滿足DRC規(guī)則才能獲得更好的DFM良率。通過(guò)使用本文提供的方法,可以解決與7nm制程節(jié)點(diǎn)相關(guān)的不同DRC違規(guī)問(wèn)題。

我們?cè)诒疚闹杏懻摰倪@些實(shí)用方法可以幫助設(shè)計(jì)師提前完成設(shè)計(jì),并有助于減少簽核階段所需的迭代次數(shù),從而加快ASIC流片和上市時(shí)間。

學(xué)習(xí)園地