POSIT是一種新興的浮點數格式,可更加高效地在不同數值范圍內分配精度。其接近0值的數據可獲得更高的計算精度,而對于極大或極小的數據值可適當舍棄一些精度以換取更大的數據表示范圍。這種動態精度分配的特性非常適合AI算法,在相同數據位寬下(如POSIT8相比INT8)能實現更好的算法性能。此前,研究者針對POSIT的特殊格式設計了高效的計算硬件,但這些設計未能充分利用POSIT尾數長度可變的特性。如能設計出一種針對POSIT變長尾數的特點、動態節省尾數乘法計算代價的策略,將可以一種算法精度損失較小的近似計算方法來降低POSIT乘法計算中占據主導的尾數乘法計算功耗。

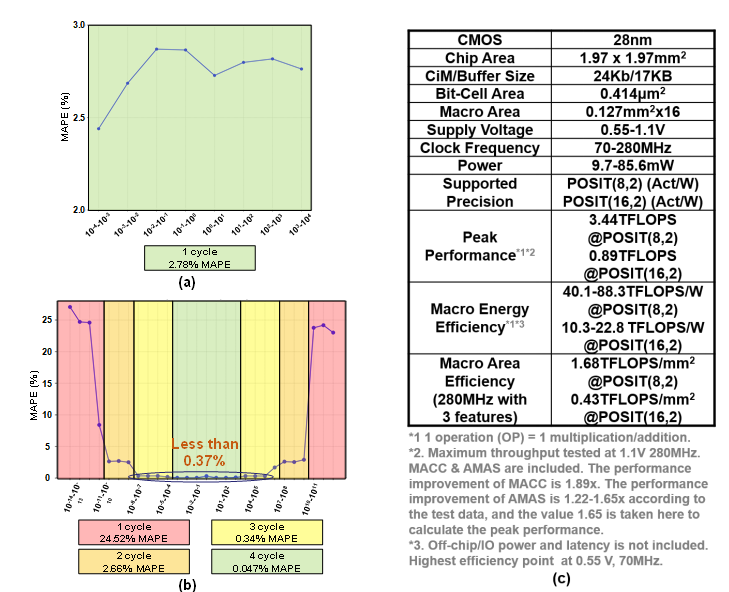

近日,中國科學院微電子研究所集成電路制造技術全國重點實驗室張鋒研究員團隊提出了一種基于動態預測POSIT結果尾數長度的SRAM存內計算宏,在較小的算法精度損失下實現吞吐率和能效的共同提升。針對POSIT的變長尾數特點,提出了一種新的數字CIM宏,其可以在執行POSIT浮點MAC計算之前確定乘法計算中尾數的哪些部分可以被舍棄。使用無符號Radix8 Booth的乘法計算邏輯電路和最終周期融合(FCF)技術,進一步減少了CIM宏的計算周期數量,并將能效提高了2.19-2.79倍。針對CIM結構無法支持計算周期靈活跳過的問題,設計了一個CIM宏級近似計算控制 (MACC) 單元來動態調整單個CIM宏的計算周期數量,實現了 1.89 倍的加速效果,而近似計算的平均絕對百分比誤差 (Mean Absolute Percentage Error,MAPE) 損失僅為 3.24%。針對尾數乘法中的稀疏bit,提出了一個激活尾數對齊跳過 (AMAS) 單元,幫助于減少稀疏激活數據的輸入周期數量,從而獲得 1.41 倍的性能提升。

本研究以“A 28-nm 88.3-TFLOPS/W POSIT-Approximate-Calculation-Based Digital Computing-in-Memory Macro Incorporating Final-Cycle Fusion and Joint-Skipping” 為題發表在集成電路設計領域旗艦期刊IEEE Journal of Solid-State Circuits上,微電子所博士研究生吳昊為第一作者、張鋒研究員與清華大學陳勇教授為通訊作者。該研究得到了科技部重點研發計劃、國家自然科學基金、中國科學院戰略先導專項等項目的支持。

全文鏈接:https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=11113258

圖1(a)不同數據區間POSIT8近似計算誤差, (b)不同數據區間POSIT16近似計算誤差, (c)芯片性能總結表格

| 相關新聞: |

| 微電子所在POSIT浮點數SRAM存內計算宏芯片領域取得進展 |

| 微電子所在芯粒集成電遷移EDA工具研究方向取得重要進展 |

| 微電子所在人工智能驅動原子級工藝仿真方向取得重要進展 |

學習園地