隨著集成電路密度提高,晶體管的工藝節(jié)點(diǎn)不斷微縮,已逼近物理極限。三維互補(bǔ)式場效應(yīng)晶體管(3D CMOS)技術(shù)成為破局的潛在路徑。傳統(tǒng)硅基3D CMOS集成技術(shù)熱預(yù)算較高,導(dǎo)致工藝復(fù)雜成本提高,并可能引發(fā)性能退化等問題,限制了其商業(yè)應(yīng)用。

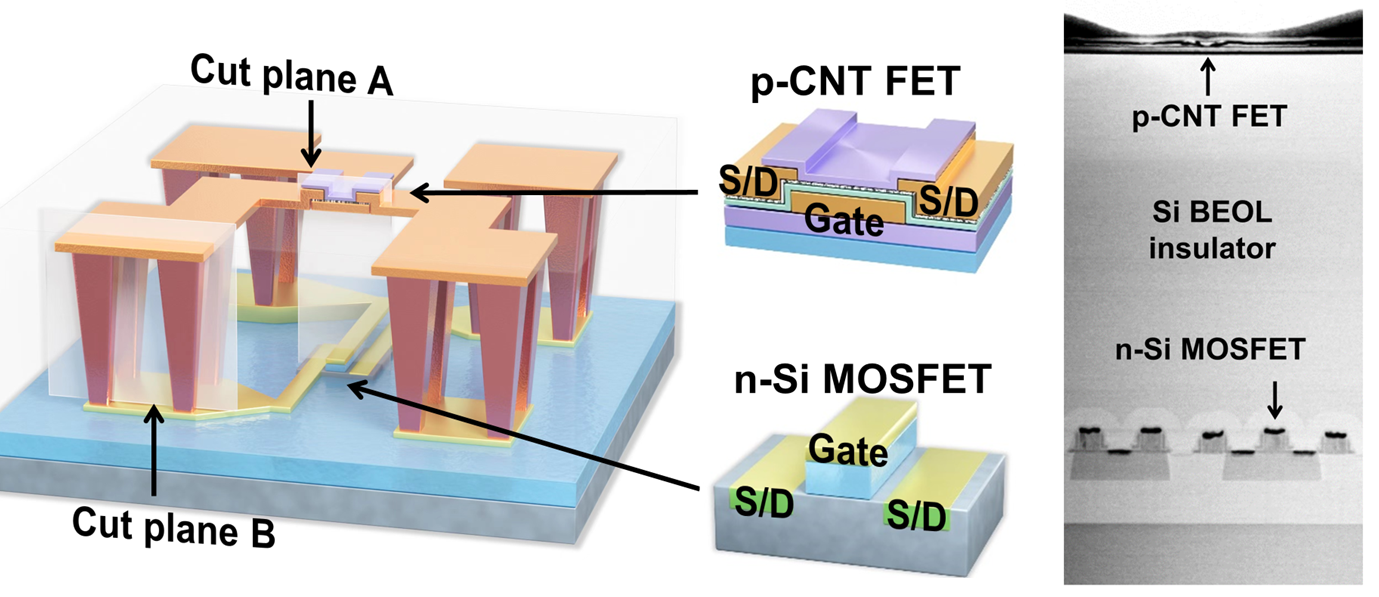

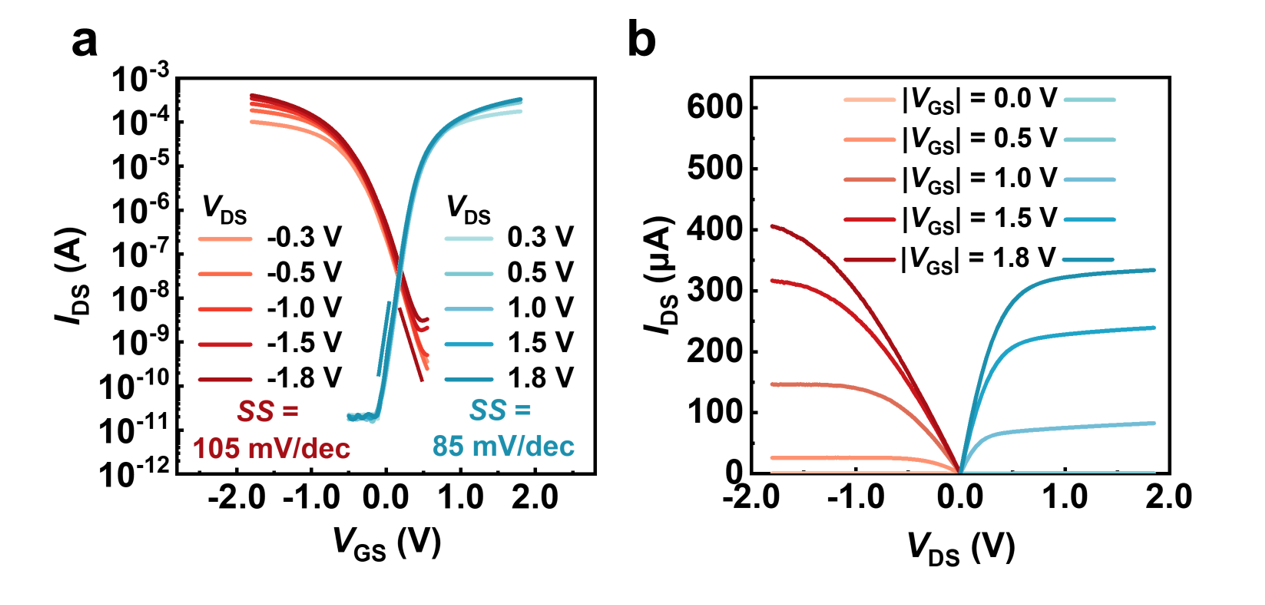

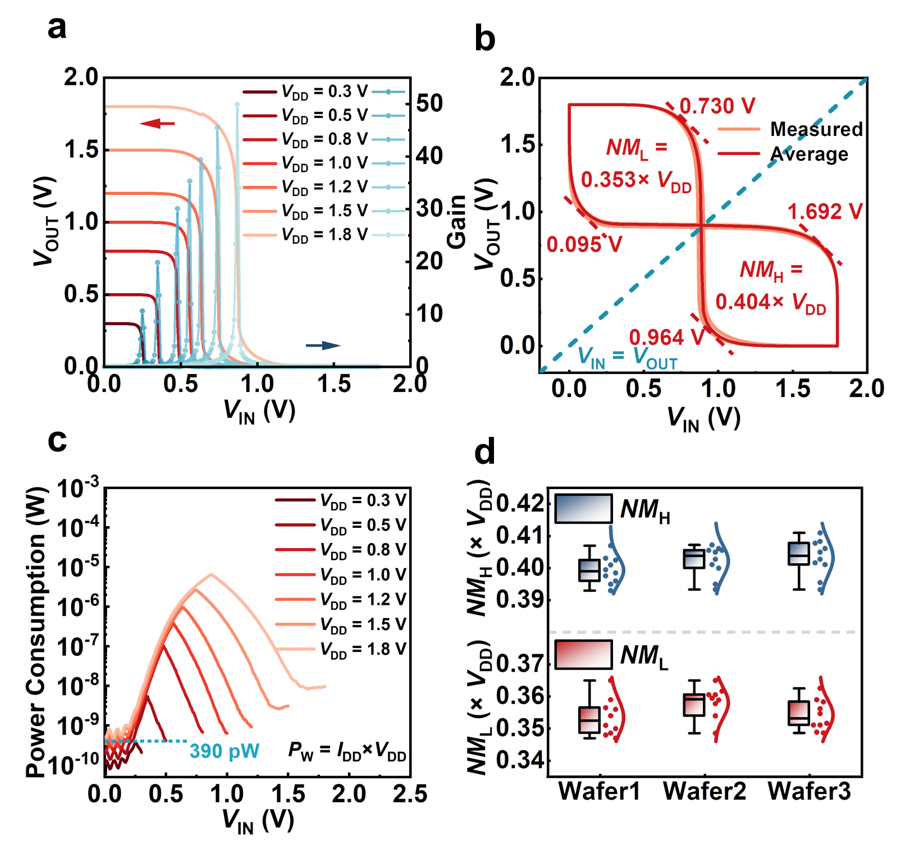

針對上述問題,中國科學(xué)院微電子研究所研究員李博與副研究員陸芃團(tuán)隊(duì),基于碳納米管材料低溫成膜能力,提出碳納米管/硅異質(zhì)集成的3D CMOS技術(shù),實(shí)現(xiàn)了180nm SOI器件后道的低溫碳納米管器件集成。該團(tuán)隊(duì)提出面向高性能數(shù)字電路應(yīng)用的工藝優(yōu)化方案,可實(shí)現(xiàn)碳納米管器件閾值電壓的精準(zhǔn)調(diào)控,可完成N、P晶體管電學(xué)特性的匹配,使3D CMOS噪聲容限提升,同時(shí)實(shí)現(xiàn)高增益、超低功耗和高均一性等優(yōu)異性能。

進(jìn)一步,為論證這一述技術(shù)在先進(jìn)工藝節(jié)點(diǎn)中的集成能力,團(tuán)隊(duì)使用TCAD仿真搭建了14nm FinFET/CNT 3D CMOS電路單元。理論分析顯示,該技術(shù)在噪聲容限和功耗方面優(yōu)于商用14nm-FinFET工藝。

相關(guān)研究成果以Low-Thermal-Budget Construction of Carbon Nanotube p-FET on Silicon n-FET toward 3D CMOS FET Circuits with High Noise Margins and Ultra-Low Power Consumption為題,發(fā)表在《先進(jìn)功能材料》(Advanced Functional Materials)上。該工作由微電子所、南京大學(xué)、安徽大學(xué)合作完成。?

圖1 碳硅三維異質(zhì)集成CMOS FET器件示意圖

圖2 碳納米管器件與硅基器件的電性匹配

圖3 碳硅CMOS FET器件電學(xué)性能表現(xiàn)

| 相關(guān)新聞: |

| 微電子所在納米森林傳感器應(yīng)用研究方面取得新進(jìn)展 |

| 微電子所利用新型堆疊納米片溝道表面處理技術(shù)研制成功接近理想開關(guān)的GAA晶體管 |

| 微電子所在多模態(tài)數(shù)據(jù)表示學(xué)習(xí)方面取得進(jìn)展 |

學(xué)習(xí)園地