環繞柵極晶體管(GAAFET)與傳統FinFET工藝流程相比,引入了內側墻(inner spacer)、溝道釋放(channel release)等工藝,必須通過對疊層結構的精確橫向刻蝕來實現。高精度刻蝕工藝控制是三維集成電路制造面臨的最大挑戰之一,其工藝機理和調控機制在科學界和工業界受到廣泛關注。

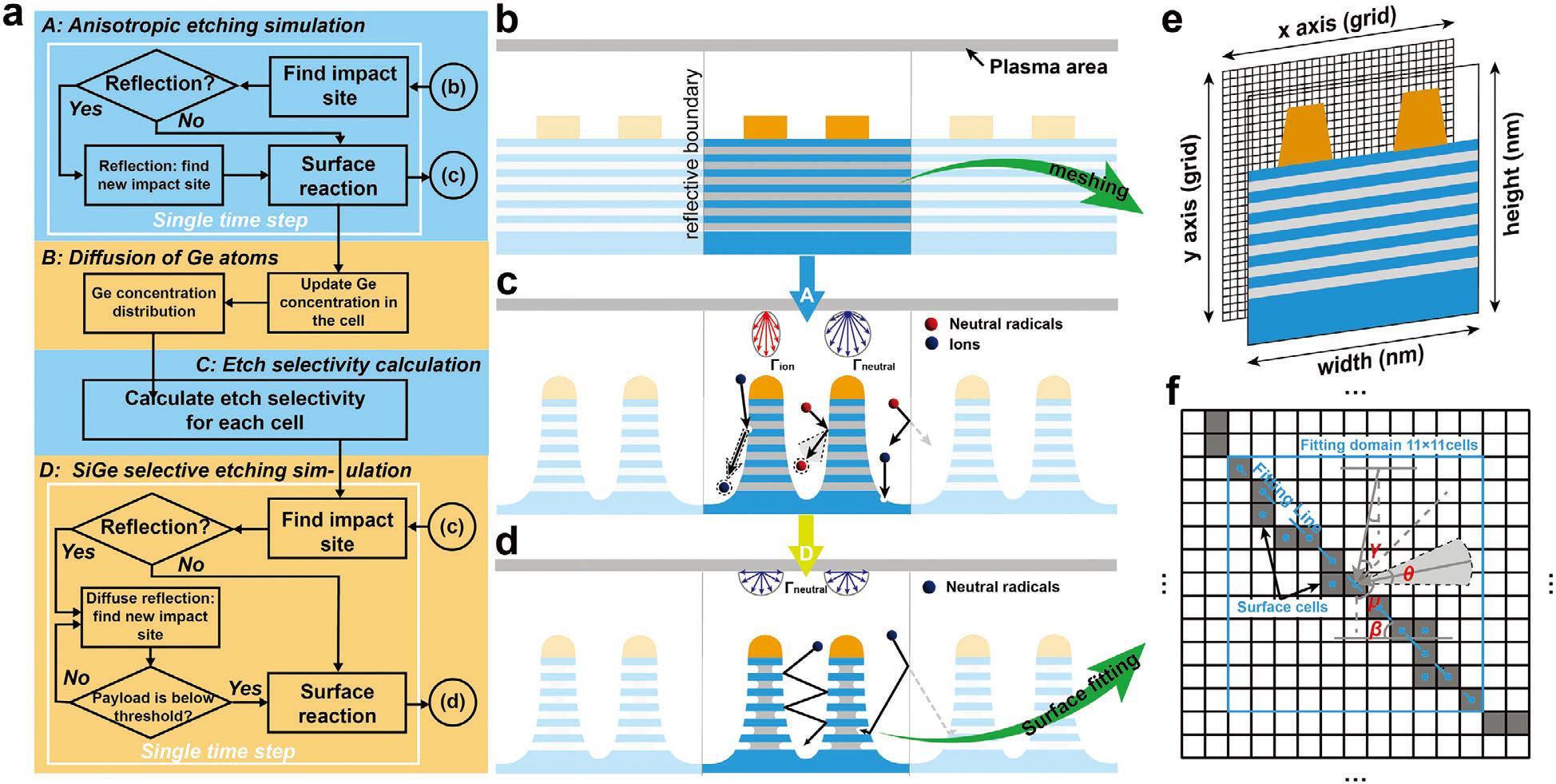

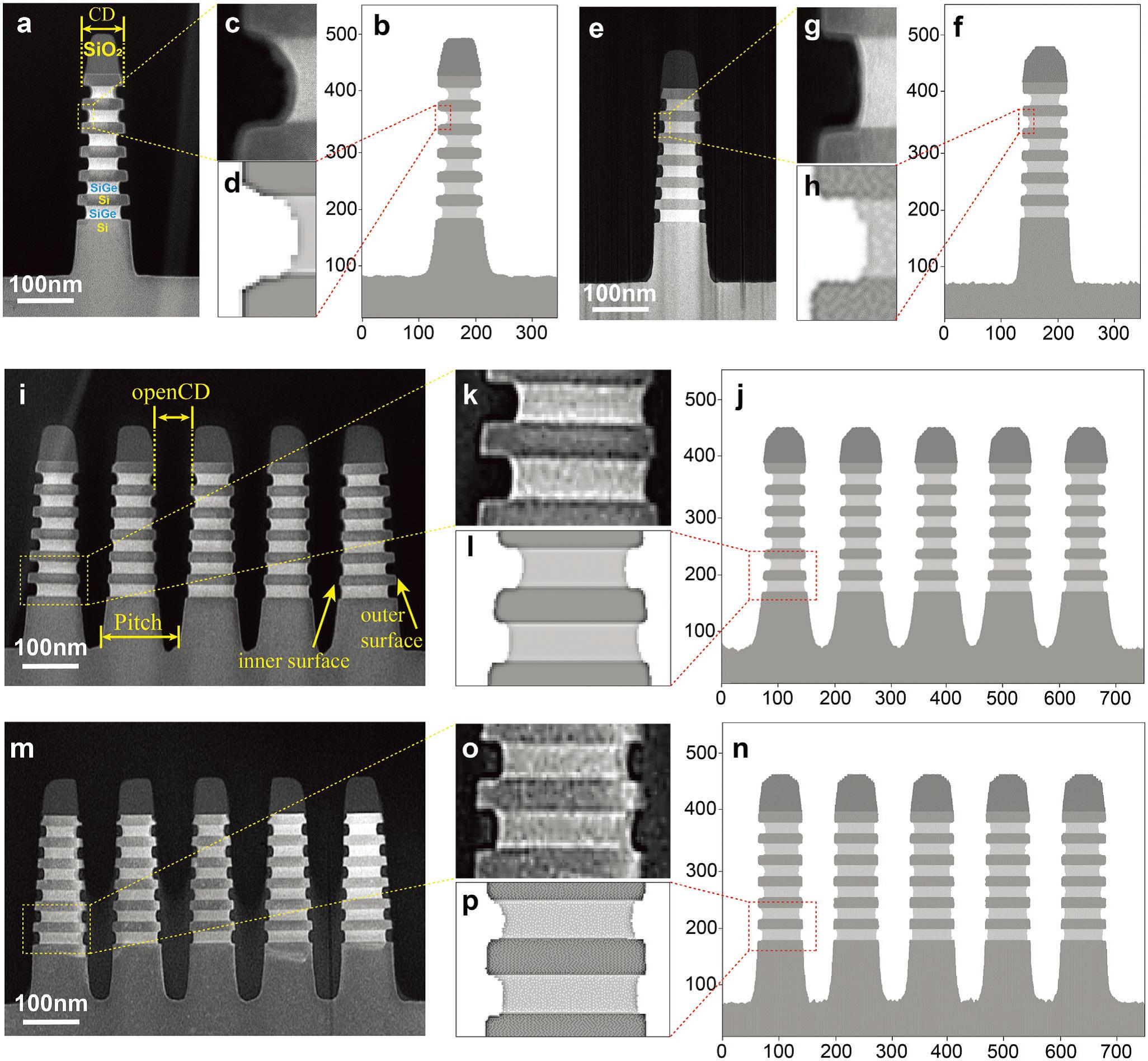

針對GAA內側墻結構Si/SiGe疊層橫向選擇性刻蝕工藝面臨的形貌缺陷和均勻性問題,微電子研究所EDA中心陳睿研究員與先導中心李俊杰高級工程師、南方科技大學王中銳教授、維也納工業大學Lado Filipovic教授合作,通過提出全新的Ge原子解吸附和擴散的模擬算法,建立了基于蒙特卡洛方法的連續兩步干法刻蝕工藝輪廓仿真模型,實現了針對Si/SiGe六疊層結構的橫向選擇性刻蝕工藝輪廓仿真,并完成了相應結構的流片實驗。通過結合形貌仿真和透射電子顯微鏡(TEM)表征,探究了Ge層刻蝕表面圓化現象,以及腔體氣壓等參數對刻蝕形貌均勻性的影響機制。該項工作為闡明新原理刻蝕工藝機理和優化工藝性能提供了理論和實驗參考。

研究成果近期以題為“A Two-Step Dry Etching Model for Non-Uniform Etching Profile in Gate-All-Around Field-Effect Transistor Manufacturing”?發表在材料領域頂級期刊《Small》上,微電子所碩士研究生呼子義為論文的第一作者,微電子所陳睿研究員、韋亞一研究員、南方科技大學王中銳教授為共同通訊作者, 同時入選TCAD仿真領域旗艦會議SISPAD 2024口頭報告。此外,相關研究成果還發表在《ACS Applied Electronic Materials》、《Journal of Vacuum Science & Technology A》?等期刊上,微電子所李俊杰高級工程師為共同通訊作者。該項研究得到了中國科學院戰略性A類先導專項、國家自然科學基金的支持。

論文鏈接:https://onlinelibrary.wiley.com/doi/10.1002/smll.202405574

圖1 建模流程

圖2 不同氣壓條件下的Si/SiGe六疊層iso/dense結構刻蝕實驗與仿真結果

| 相關新聞: |

| 微電子所在光子集成激光探感技術方面取得進展 |

| 微電子所在存內計算實現語義記憶動態神經網絡方面取得進展 |

| 微電子所在GaN器件研究方面取得重要進展 |

學習園地