當前,基于邊緣智能計算設備運行的人工智能應用日趨復雜及高精度,為降低邊緣設備運行的延遲和功耗,存算一體技術被應用在邊緣設備端,通過減小數(shù)據(jù)搬運的開銷最大化減少邊緣設備上的延遲與功耗。但傳統(tǒng)的存算一體宏僅支持使用整數(shù)型數(shù)據(jù)計算,難以支持日趨高精度、高復雜度以及片上訓練的邊緣端智能計算任務。且僅使用單一模擬或數(shù)字方案的存算一體宏,在能量效率、面積效率和精度上難以取得最優(yōu)化。如何有效結合模擬存算與數(shù)字存算模式優(yōu)勢,在總體上取得更高的能量效率和面積效率,同時盡可能保證高精度,以及如何探索數(shù)模混合方案的設計空間,仍然是存算一體宏領域繼續(xù)解決的問題。

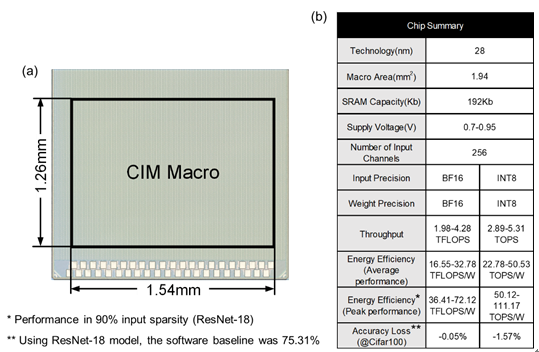

針對以上問題,中國科學院微電子研究所劉明院士團隊研發(fā)出基于外積運算的數(shù)模混合存算一體宏芯片,設計了一種數(shù)模混合浮點 SRAM 存內計算方案,提出了模擬與數(shù)字存算宏的混合方法,結合了使用模擬存算方案進行高效陣列內位乘法和使用數(shù)字存算方案進行高效陣列外多位移位累加的優(yōu)點,達到整體上高能量效率與面積效率。通過殘差式數(shù)模轉換器架構,使數(shù)模轉換器所需分辨率僅為輸入位精度的對數(shù),實現(xiàn)了高吞吐率和低開銷。通過基于矩陣外積計算數(shù)學原理的浮點/定點存算塊架構,矩陣-矩陣-向量計算可通過累加器元件完成。同之前的數(shù)字存算方案使用矩陣內積原理的大扇入、多級加法器樹相比,吞吐率更高。該架構還支持細粒度的非結構激活稀疏性以進一步提升總體能效。該存算一體宏芯片在28nm ?CMOS工藝下流片,可支持BF16浮點精度運算以及INT8定點精度運算,BF16浮點矩陣-矩陣-向量計算峰值能效達到了72.12TFLOP/W,INT8定點矩陣-矩陣-向量計算峰值能效達到了111.17TFLOP/W。這一研究結果為采用數(shù)模混合方案的存算一體架構芯片提供了新思路。

近期,本工作以“A 28nm 72.12TFLOPS/W Hybrid-Domain Outer-Product Based Floating-Point SRAM Computing-in-Memory Macro with Logarithm Bit-Width Residual ADC”為題發(fā)表在 ISSCC 2024國際會議上,微電子所博士生袁易揚為第一作者,張鋒研究員與北京理工大學王興華教授為通訊作者。該研究得到了科技部重點研發(fā)計劃、國家自然科學基金、中國科學院戰(zhàn)略先導專項等項目的支持。

28nm 基于外積的數(shù)模混合浮點存算一體宏芯片:(a)芯片顯微鏡照片,(b)芯片特性總結表

| 相關新聞: |

| 微電子所在片上學習存算一體芯片方面取得重要進展 |

| 微電子所在IGZO 2T0C DRAM多值存儲領域取得重要進展 |

| 微電子所在鉿基鐵電存儲器芯片研究領域取得重要進展 |

學習園地