摩爾定律推動了持續50年的集成電路的發展,然而,時至今日,由于物理極限的限制,晶體管的進一步微縮已經舉步維艱。為了進一步增加集成電路性價比,一些基于新原理、新材料、新工藝的晶體管不斷被提出,其中負電容場效應晶體管是近年來被廣泛研究的對象之一。負電容晶體管可以克服“玻爾茲曼熱限制”,即在室溫下突破亞閾值擺幅60mV/decade的最低限制,降低電源電壓和電路功耗,有望被應用于3nm及以下技術節點。

由于負電容晶體管理論的復雜性,對負電容晶體管以及由其構建的電路特性的理論研究至關重要。近日,中科院微電子所先導中心朱慧瓏研究員課題組在英國皇家物理學會《Semiconductor Science and Technology》上發表了文章:Investigation of Device-Circuit for Negative Capacitance Vertical Nanowire FETs Based on SPICE Model

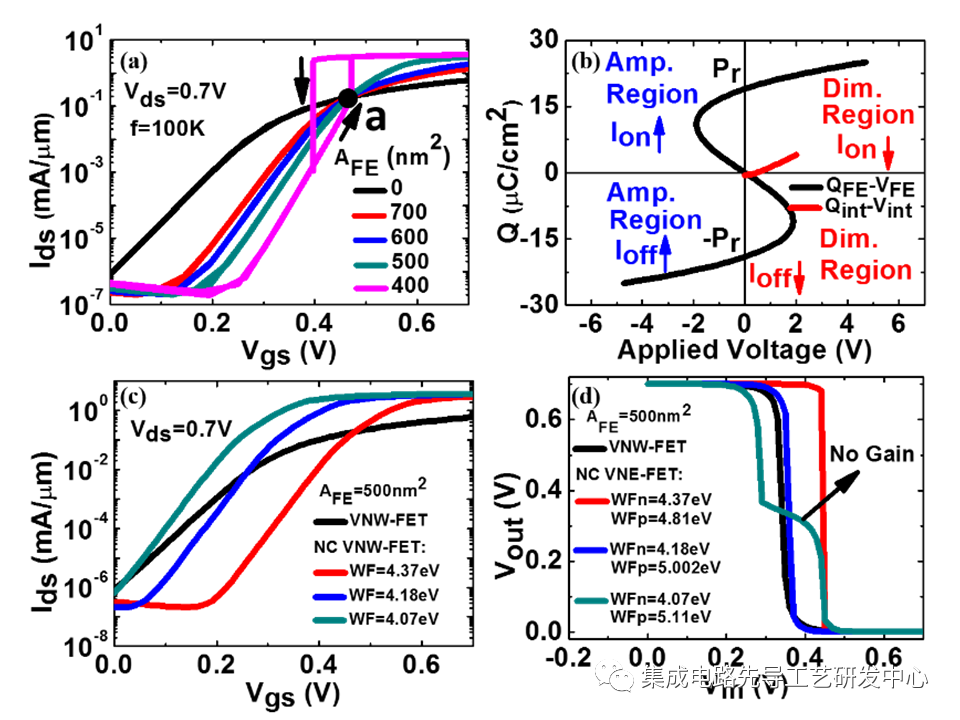

文章中,如圖1.(a)中點“a”代表負電容自由能關系中的不穩定點,在該點極化方向開始轉變,導致了晶體管電流的增大或減小。因此晶體管閾值電壓調節到點“a”位置時,將獲得最佳的器件性能。圖1.(b)展示了負電容晶體管的四個工作區域,當負電容晶體管工作在第二和第四象限時,將會獲得較佳的器件性能。圖1.(c)-(d)展示了金屬柵功函數對負電容晶體管以及由其構建的CMOS反相器電路特性的影響。文章指出,當負電容晶體管閾值電壓過小時,會造成由其構建的CMOS反相器電路增益的嚴重損失。因此,對于由負電容晶體管構建的集成電路,需要進行電路和器件的協同設計。

圖1.(a)不同負電容面積下的負電容晶體管的Ids-Vgs特性,(b)“S曲線”的四個工作區域,(c)不同金屬柵功函數下的負電容晶體管的Ids-Vgs特性,(d)不同金屬柵功函數下的CMOS反相器的特性。

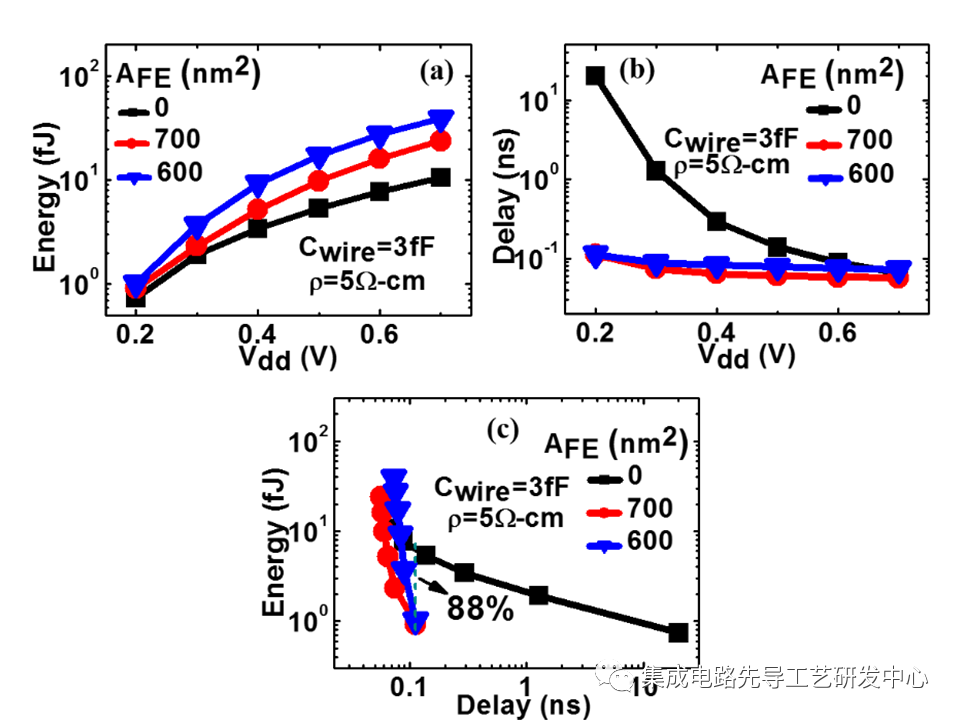

圖2.(a)-(c)展示了基于負電容晶體管構建的7階環形振蕩器電路的能量消耗以及傳播延時的特性。結果顯示,由于負電容晶體管具有更大的柵極電容,因此由其構建的環形振蕩器具有更大的動態能量消耗(圖2.(a)),然而更大的驅動電流使其擁有更小的傳播延時(圖2.(b))。此外,通過能量-延時關系分析,在電源電壓較小的條件下,電路面積相同時,相同的能量消耗下,負電容晶體管具有更小的傳播延時;相同的延時下,負電容晶體管具有更小的能量消耗。

圖2. 7

| 相關新聞: |

| 微電子所在先進Co互連阻擋層研究領域取得進展 |

| STT-MRAM器件與集成技術研究 |

學習園地