成果展示

微電子所在低功耗模數(shù)轉(zhuǎn)換器研究領(lǐng)域取得重大進(jìn)展

近日,微電子所智能感知研發(fā)中心樊曉華研究員團(tuán)隊(duì)成功研發(fā)出一款13位 50MS/s的混合型模數(shù)轉(zhuǎn)換器(ADC),品質(zhì)因數(shù)(FOM)達(dá)到國(guó)際領(lǐng)先水平。

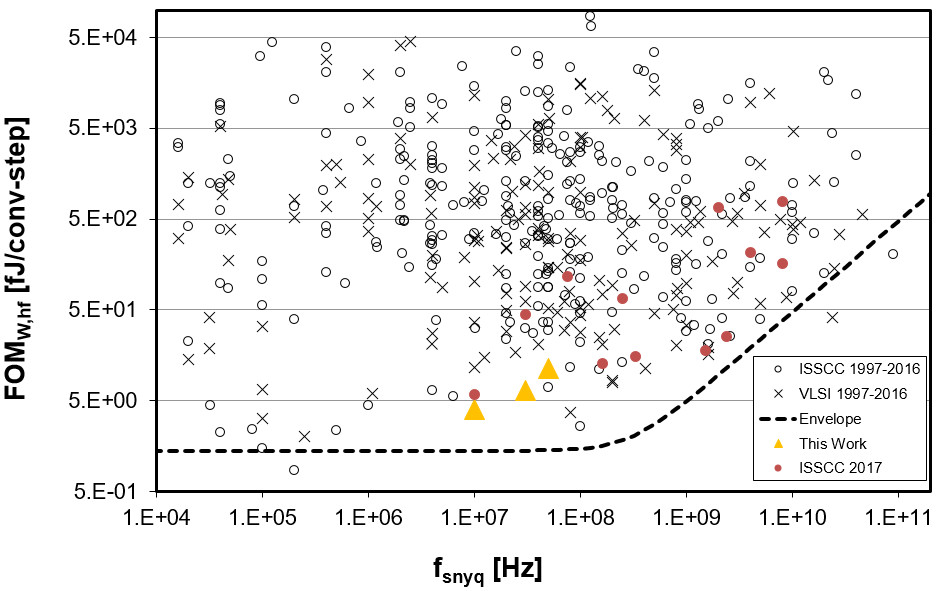

該款A(yù)DC采用了基于量程輔助、逐次逼近、流水線等技術(shù)的混合型架構(gòu),在國(guó)際上首次提出高增益(32倍)PVT不敏感的時(shí)間域放大器,顯著降低了ADC的功耗及校準(zhǔn)算法復(fù)雜度,提出了量程輔助的懸空電容陣列開關(guān)算法及預(yù)開窗異步控制邏輯,提高了ADC的轉(zhuǎn)換速率。該ADC在130nm CMOS工藝下流片成功,有效核心面積0.22 mm2。測(cè)試結(jié)果表明,在1.2 V供電、50 MS/s轉(zhuǎn)換速率下,輸入信號(hào)為2 MHz時(shí),ADC的信噪失真比(SNDR)達(dá)71.6 dB,無(wú)雜散動(dòng)態(tài)范圍(SFDR)達(dá)84.6 dB。該ADC支持可變電源電壓與轉(zhuǎn)換速率,當(dāng)電源電壓從0.8 V變化到1.2 V時(shí),ADC的轉(zhuǎn)換速率為10-50 MS/s,Walden FOM值為4.0-11.3 fJ/conversion-step。

此項(xiàng)工作主要由樊曉華研究員、張明磊博士完成,得到了美國(guó)德克薩斯農(nóng)工大學(xué) Edgar Sánchez-Sinencio教授的支持。該款A(yù)DC可滿足當(dāng)前高速發(fā)展的片上集成系統(tǒng)對(duì)低功耗、高速度以及高精度等特性的嚴(yán)格要求,可運(yùn)用于多種便攜式通信系統(tǒng)的應(yīng)用場(chǎng)景。相關(guān)研究成果已被國(guó)際頂級(jí)期刊 IEEE Journal of Solid State Circuits 接收。

圖1. ADC芯片照片

圖2. 不同模式下SFDR/SNDR隨輸入頻率的變化

圖3. FOM值與國(guó)際頂級(jí)會(huì)議(ISSCC/VLSI)的比較