在半導體存儲技術領域,DRAM作為計算系統(tǒng)的關鍵組成部分,一直面臨著提升密度與降低功耗的雙重挑戰(zhàn)。隨著人工智能與大數(shù)據(jù)的快速發(fā)展,傳統(tǒng)存儲架構已難以滿足日益增長的數(shù)據(jù)處理需求。在主流1T1C架構中,制程微縮導致存儲電容難以進一步縮小,電容器漏電與干擾問題日益凸顯。2T0C架構雖被視為潛在解決方案,但傳統(tǒng)集成方法因采用分步堆疊工藝,面臨著橫向對準偏差與熱循環(huán)效應帶來的嚴苛挑戰(zhàn)。

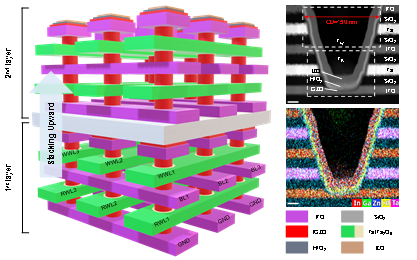

針對上述挑戰(zhàn),微電子所集成電路制造技術全國重點實驗室研究團隊聯(lián)合北京超弦存儲器研究院、山東大學提出一種新型雙柵4F2 2T0C存儲單元。該技術通過原位金屬自氧化工藝,實現(xiàn)4F2存儲單元中讀取晶體管和寫入晶體管的自對準集成,并可通過多值存儲技術進一步提升存儲密度。測試結果表明,該垂直雙柵晶體管實現(xiàn)了優(yōu)異的開態(tài)電流與亞閾值擺幅,并在85℃熱穩(wěn)定性測試中取得-22.6 mV(NBTS)與87.7 mV(PBTS)的可靠表現(xiàn),兼具高性能與高穩(wěn)定性。基于該晶體管的4F2 2T0C單元支持4比特多值存儲,實現(xiàn)了50納秒的寫入時間,數(shù)據(jù)保持時間超過300秒,展現(xiàn)出良好的技術潛力。

本研究以“High-density three-dimensional integration of dynamic random-access memory using vertical dual-gate IGZO TFTs”為題發(fā)表在Nature Communications期刊上,微電子所博士后廖福錫、北京超弦存儲器研究院朱正勇研究員、微電子所博士生李子涵為共同第一作者,微電子所李泠研究員、楊冠華副研究員、北京超弦存儲器研究院趙超研究員、山東大學Arokia Nathan教授為共同通訊作者。

該項研究得到了重點研發(fā)計劃、國家自然科學基金等項目的支持。

圖1.?4F2雙柵2T0C存儲陣列示意圖和電鏡表征

綜合信息