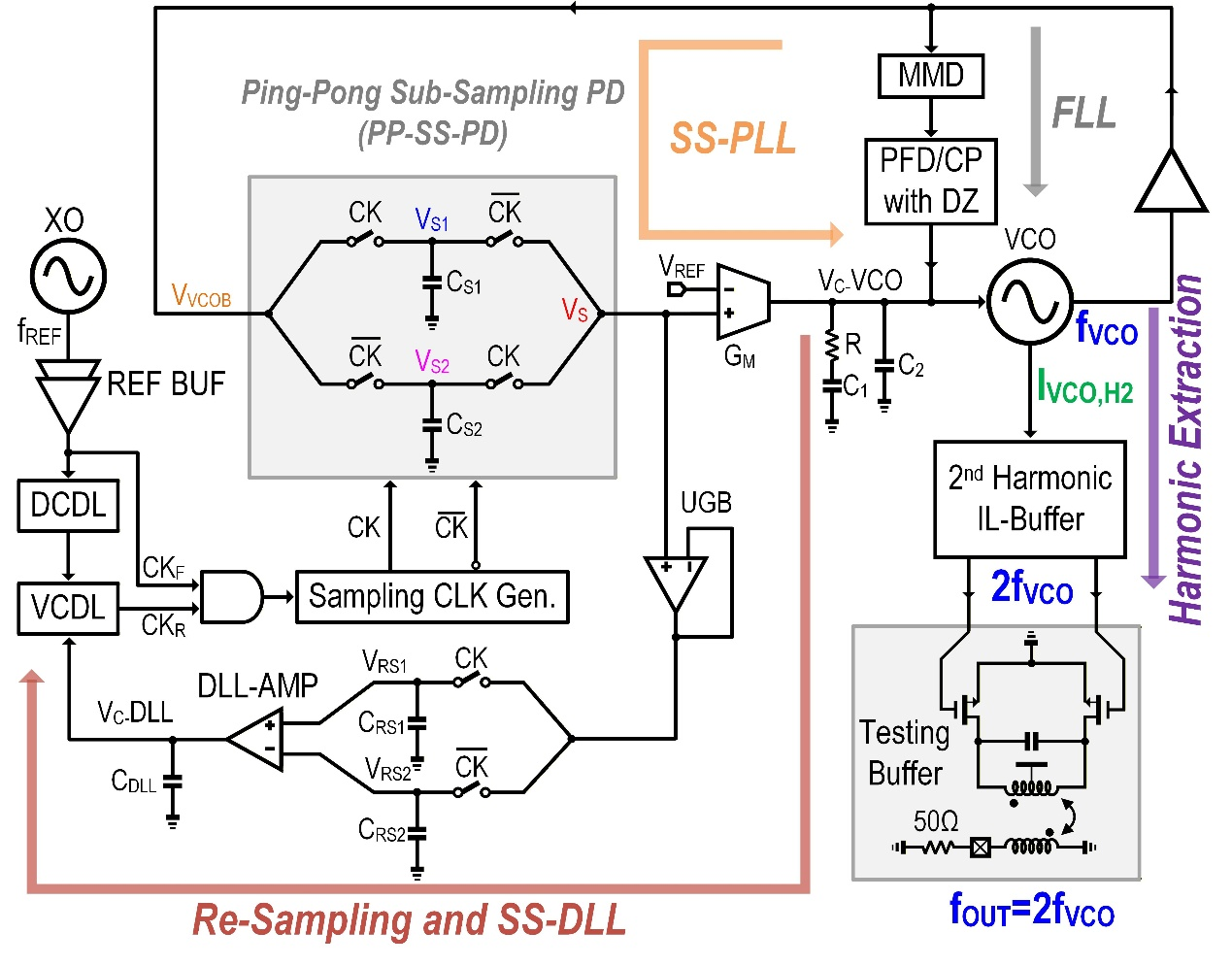

5.5G/6G 無(wú)線通信技術(shù)的迭代演進(jìn)及下一代 Serdes 接口向更高傳輸速率突破,對(duì)毫米波本振時(shí)鐘的抖動(dòng)性能提出了更嚴(yán)苛的要求。亞采樣鎖相環(huán)憑借其高鑒相增益的固有優(yōu)勢(shì),已成為低抖動(dòng)時(shí)鐘芯片的主流解決方案。但傳統(tǒng)亞采樣鑒相器中存在的電荷共享效應(yīng)嚴(yán)重惡化環(huán)路相位裕度,需大幅增加主從采樣電容比值,導(dǎo)致隔離緩沖器功耗上升。同時(shí),為抑制二進(jìn)制頻移鍵控效應(yīng)對(duì)參考雜散的影響,傳統(tǒng)結(jié)構(gòu)需引入額外的dummy采樣路徑,造成功耗開(kāi)銷(xiāo)進(jìn)一步上升。此外,在毫米波頻段,電容與變?nèi)莨艿钠焚|(zhì)因數(shù)較低,造成振蕩器相位噪聲惡化,影響鎖相環(huán)的整體抖動(dòng)性能。

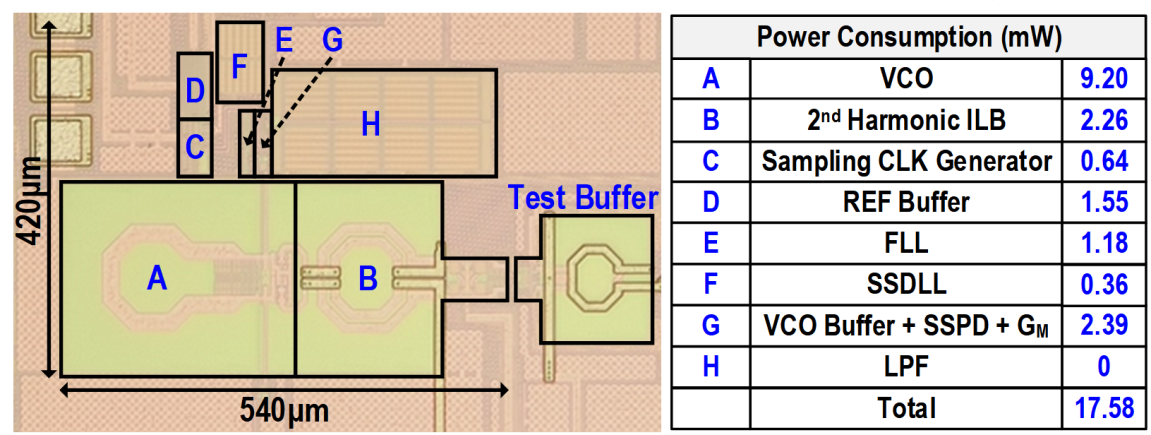

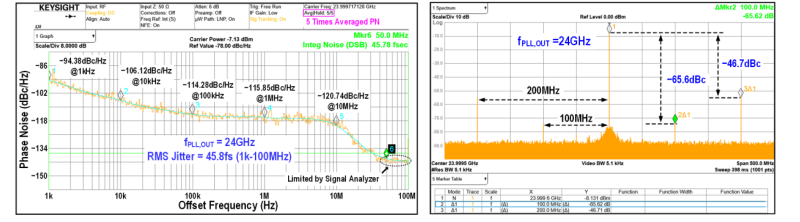

針對(duì)上述關(guān)鍵問(wèn)題,微電子所抗輻照器件技術(shù)重點(diǎn)實(shí)驗(yàn)室楊尊松、黃云波團(tuán)隊(duì)與清華大學(xué)合作,提出了一種雙邊沿乒乓亞采樣鎖相環(huán)架構(gòu)。該架構(gòu)同時(shí)利用參考時(shí)鐘的上升沿與下降沿,實(shí)現(xiàn)參考頻率的等效倍頻,有效解決了傳統(tǒng)亞采樣鎖相環(huán)在環(huán)路帶寬、帶內(nèi)相位噪聲與參考雜散之間存在的設(shè)計(jì)折衷難題。團(tuán)隊(duì)還提出一種高功率與面積效率的注入鎖定緩沖器方案,該結(jié)構(gòu)在高效提取振蕩器二次諧波的同時(shí)能夠?qū)崿F(xiàn)諧波整形,顯著降低了鎖相環(huán)的帶外相位噪聲。基于上述兩種技術(shù),團(tuán)隊(duì)采用65nm CMOS工藝設(shè)計(jì)實(shí)現(xiàn)了一款K波段鎖相環(huán)時(shí)鐘芯片,輸出頻率覆蓋22.4–25.6 GHz,整體功耗低于18 mW,RMS積分抖動(dòng)優(yōu)于50 fs,其抖動(dòng)-功耗優(yōu)值(FoM)達(dá)到?254 dB以下。

該工作得到了國(guó)家自然科學(xué)基金的支持,研究成果以“A 22.4–25.6 GHz Ping-Pong Sub-Sampling PLL Featuring Unified Supply Voltage Level and Balanced 2nd Harmonic Extraction”為題,發(fā)表于集成電路設(shè)計(jì)領(lǐng)域頂級(jí)期刊《IEEE固態(tài)電路學(xué)報(bào)》(IEEE Journal of Solid-State Circuits)。微電子所副研究員黃云波為論文第一作者。

論文鏈接:https://ieeexplore.ieee.org/document/11227144

圖1?乒乓亞采樣鎖相環(huán)電路結(jié)構(gòu)

圖2 鎖相環(huán)芯片照片及各模塊功耗

圖3?鎖相環(huán)芯片相位噪聲及參考雜散測(cè)試性能

綜合信息