全環繞柵(GAA)器件具有極佳的柵控特性、更高的驅動性能以及更多的電路設計靈活性,是主流集成電路制造繼FinFET之后的核心晶體管結構。目前,三星電子(Samsung)、臺積電(Intel)與因特爾(TSMC)已經或者即將在3納米及以下技術節點采用該器件進行工藝量產。但其被內側墻隔開的堆疊納米片溝道會導致非連續源漏選擇外延進而產生大量缺陷,引起源漏應變減弱與驅動電流退化,造成較嚴重的源漏寄生電阻效應,成為其面向高性能電路應用的關鍵挑戰。

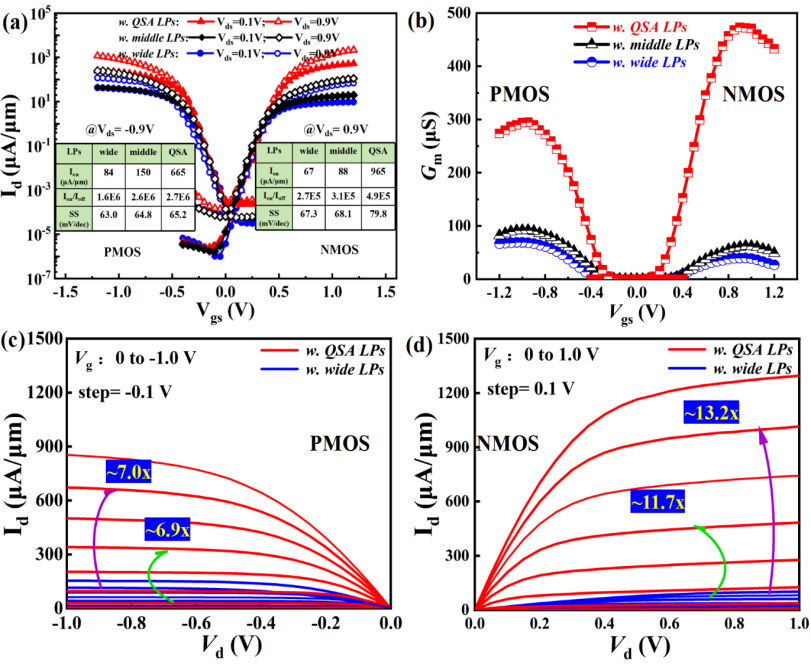

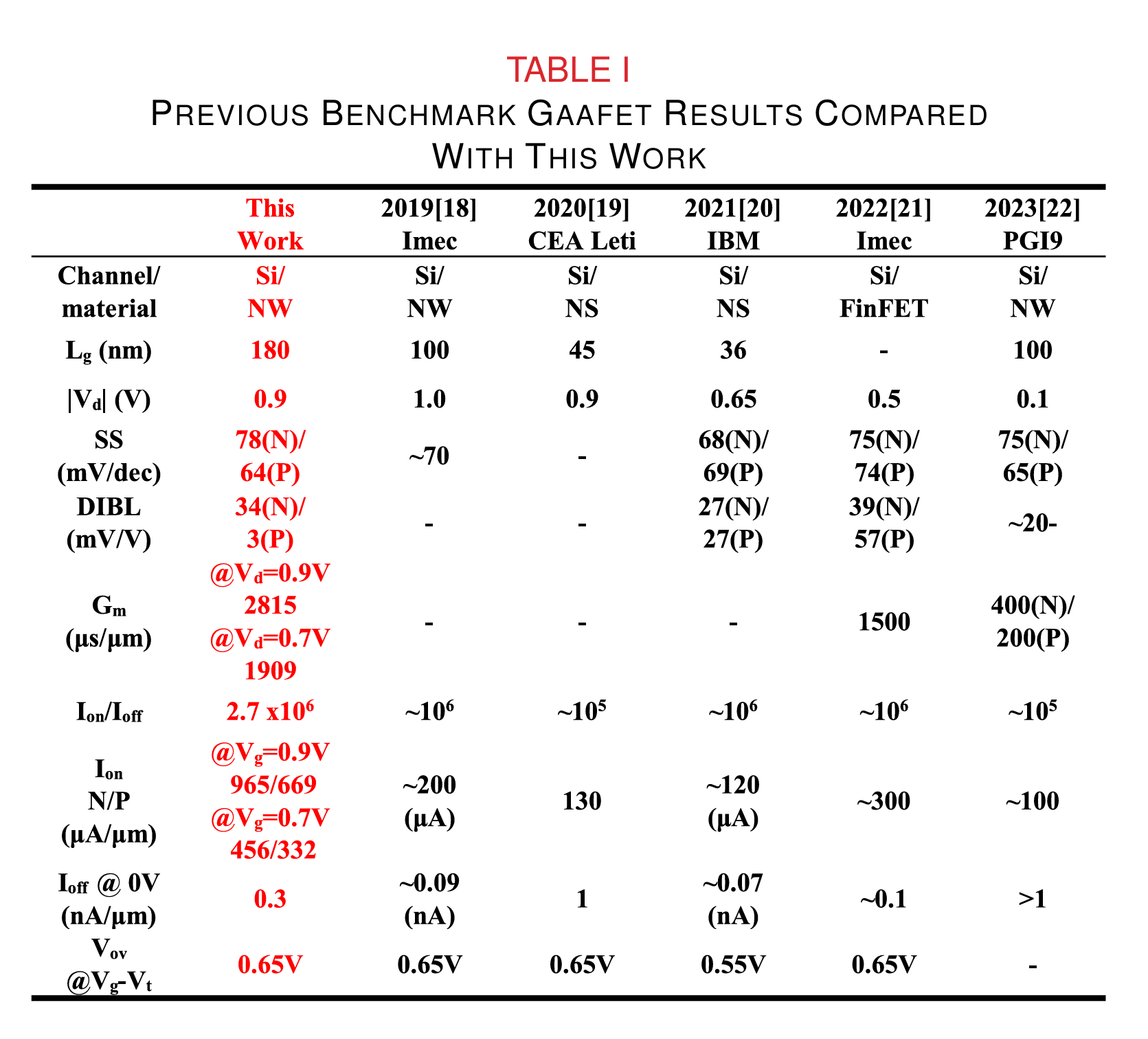

為了突破GAA 器件中嚴重的源漏選擇外延缺陷產生的高寄生電阻和低驅動性能挑戰,微電子所集成電路先導工藝研發團隊提出了一種與GAA制造工藝兼容的近自對準支撐臺(Quasi-Self-Aligned Landing Pads)技術,實現GAA器件中多層堆疊納米片溝道和單晶 SiGe/Si 超晶格源極/漏極(SD)結構之間的無缺陷連接,同時避免離子注入摻雜引起的源漏缺陷與多晶態。實驗結果表明,采用 QSA LPs 技術的 GAA器件的寄生 SD 電阻 (RSD)降低至100Ω,開態電流 (Ion) 值達到 965 μA/μm,達到世界先進水平(見表1),為高性能GAA電路應用提供了一種創新技術方案。

基于本研究成果的論文“High-Performance Gate-All-Around FETs with 100 Ω Parasitic Resistance and 965 μA/μm On-State Current using Quasi-Self-Aligned Landing Pads”(DOI: 10.1109/LED.2024.3505926)近期發表在IEEE Electron Device Letters期刊上,微電子所研究生蔣任婕為第一作者,張青竹研究員和殷華湘研究員為該文共同通訊作者。該項研究得到了中國科學院戰略性先導專項(A類)、國家自然科學基金的支持。

論文鏈接:https://ieeexplore.ieee.org/document/10767246

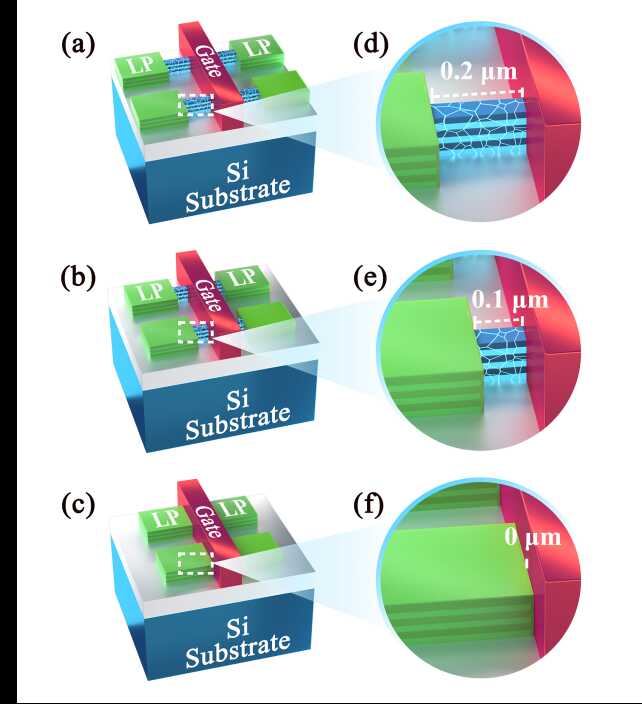

圖1 傳統GAA和采用近自對準支撐臺技術的器件結構

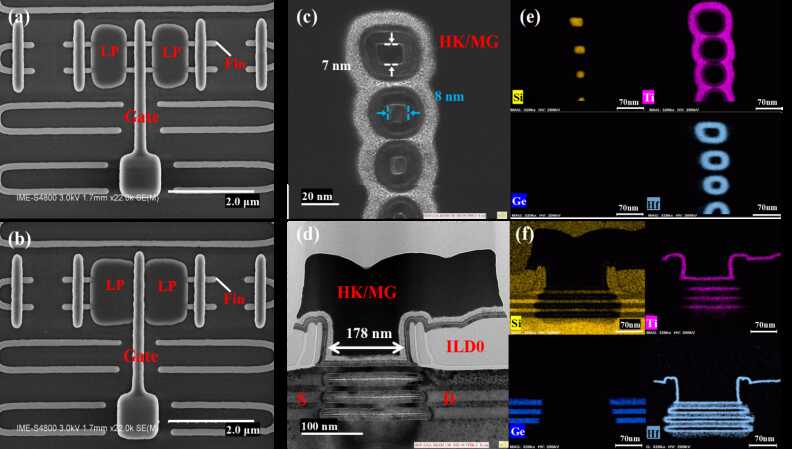

圖2 傳統GAA和采用近自對準支撐臺技術的器件結構與電學特性對比

表1 ?近年來GAA器件特性參數對比

綜合信息