近日,2024 IEEE Symposium on VLSI Technology & Circuits在美國召開,微電子所抗輻照器件技術(shù)重點實驗室李博研究員、楊尊松研究員團隊在會上展示了高性能鎖相環(huán)芯片的最新研究進展。

網(wǎng)路數(shù)據(jù)交互量爆炸式增長,促使通信技術(shù)的不斷進步,5.5G、6G、224Gb/s高速接口電路等新一代通信系統(tǒng)要求鎖相環(huán)頻率綜合器的RMS抖動小于50fs,這在硅基CMOS集成電路設(shè)計中極具挑戰(zhàn)。

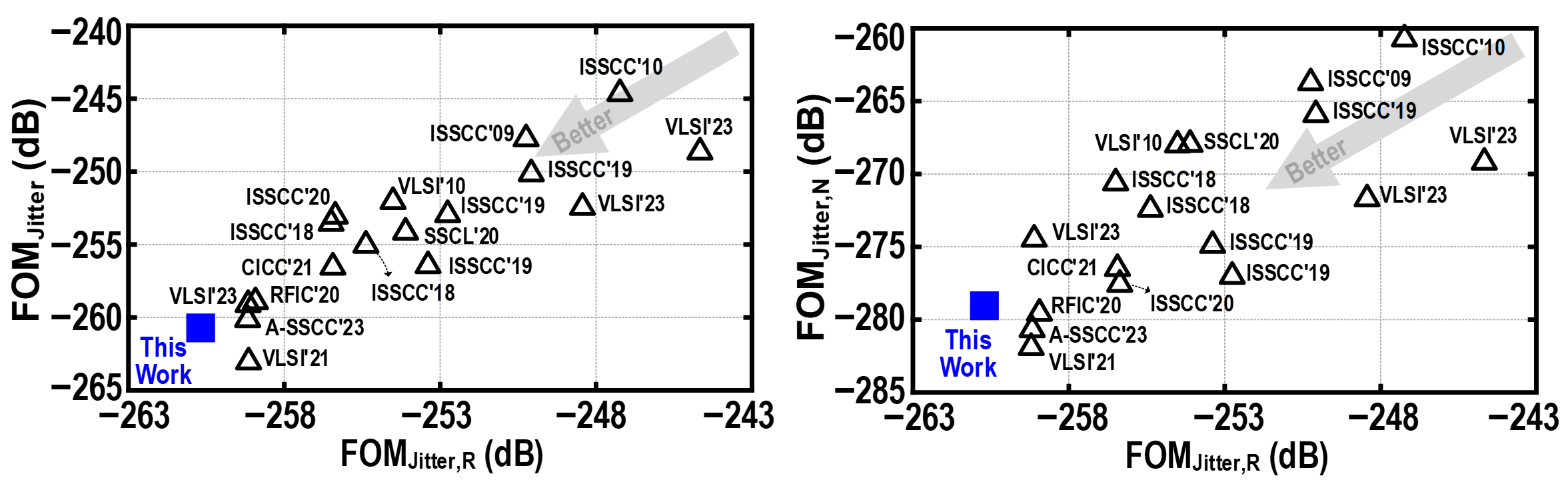

亞采樣鎖相環(huán)的相位鎖定環(huán)路無需使用多模分頻器和重定時器,有潛力在低功耗下進一步提升抖動性能。對于50fs以下極低RMS抖動,參考路徑中的緩沖器通常會極大限制亞采樣鎖相環(huán)的帶內(nèi)相位噪聲,需要消耗較大功耗和面積將其降低至較低水平。雙邊沿采樣鑒相技術(shù)能夠?qū)⒖季彌_器引入的相位噪聲降低3dB,但會惡化頻率分辨率。針對上述問題,抗輻照器件技術(shù)重點實驗室研究團隊提出了可配置雙邊沿亞采樣鎖相環(huán)結(jié)構(gòu),通過奇偶采樣模式切換,能夠在同步實現(xiàn)低功耗和低抖動的前提下保持頻率分辨率不變,所提出的鎖相環(huán)結(jié)構(gòu)在硅基65nm CMOS工藝上進行了流片驗證,實現(xiàn)了目前國際上最佳的抖動-功耗的參考頻率歸一化優(yōu)值。

????上述研究成果以“A 6.5-to-6.9-GHz SSPLL with Configurable Differential Dual-Edge SSPD Achieving 44-fs RMS Jitter, ?260.7-dB FOMJitter, and ?76.5-dBc Reference Spur”為題發(fā)表在集成電路設(shè)計領(lǐng)域國際頂級會議2024 VLSI Technology and Circuits,微電子所博士研究生陳天樂和任洪宇為該文章的共同第一作者,微電子所楊尊松研究員、李博研究員為該文章的通訊作者。

圖1. 提出的雙邊沿亞采樣鎖相環(huán)電路結(jié)構(gòu)

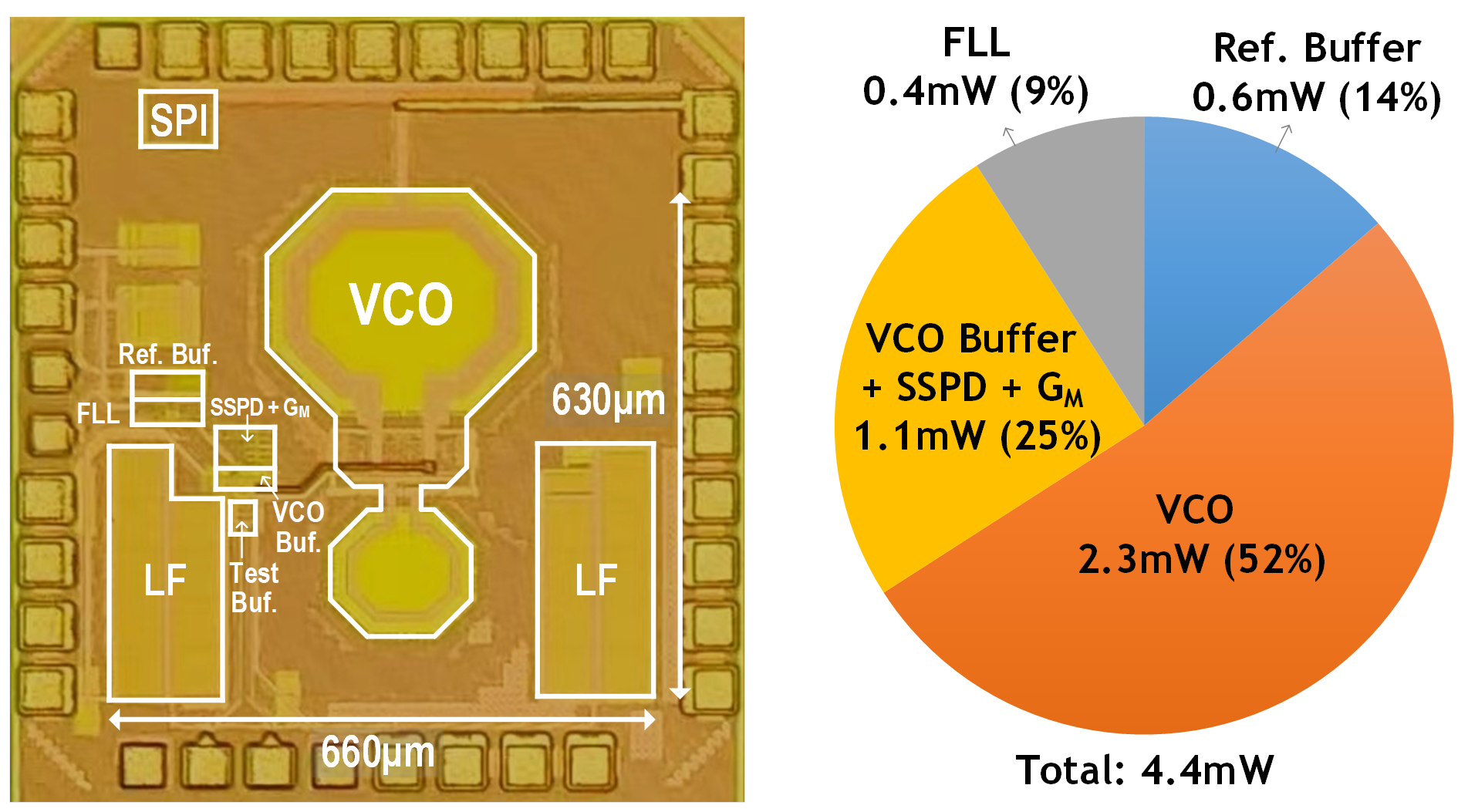

圖2 芯片照片及各個模塊的功耗占比

圖3 國內(nèi)外鎖相環(huán)性能對比

綜合信息