人工智能的飛速發(fā)展對計算和存儲等硬件資源提出了巨大需求,迫切需要提升存儲器層級訪問的性能與效率。當前,主流計算硬件的存儲系統(tǒng)由片上靜態(tài)隨機訪問存儲器(SRAM)以及片下隨機動態(tài)存儲器(DRAM)構成,它們之間通過有限的總線來進行數(shù)據(jù)傳遞,導致帶寬有限、功耗與延遲較大等問題,逐漸成為大數(shù)據(jù)、高算力等人工智能應用的瓶頸。此外,傳統(tǒng)硅基六晶體管型(6-T)SRAM單元因其較大的特征尺寸和待機漏電問題,在密度和能耗方面存在諸多限制。同時,傳統(tǒng)的硅基DRAM單元也面臨著數(shù)據(jù)保持時間較短、無法通過后道集成提升存儲密度等問題,這些問題從根本上限制了SRAM-DRAM存儲系統(tǒng)的功耗與密度。

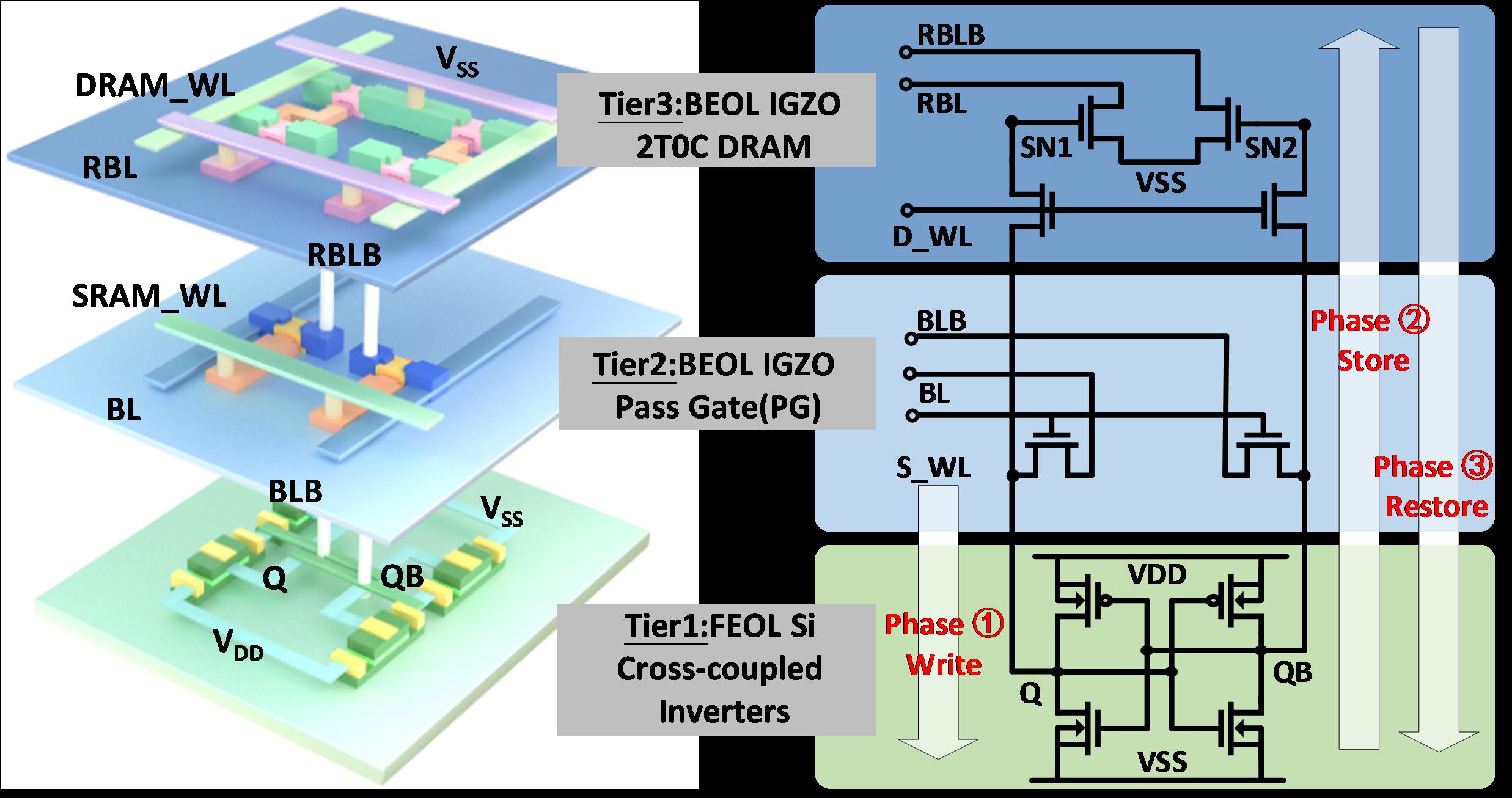

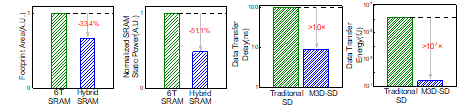

針對上述問題,微電子所集成電路制造技術重點實驗室劉明院士/李泠研究員團隊通過多層堆疊IGZO薄膜晶體管(TFT)與硅基電路后道集成,提出了一種新型IGZO/Si SRAM和IGZO 2T0C DRAM的三維存儲結構,成功實現(xiàn)了高密度、低能耗和高速數(shù)據(jù)傳輸?shù)忍匦浴T谠摻Y構中,通過在前道硅基閂鎖結構上后道集成IGZO傳輸門,有效地減少了SRAM的占用空間和待機功耗。此外,基于垂直堆疊三層間互連結構,實現(xiàn)了SRAM-DRAM數(shù)據(jù)傳輸?shù)淖畹脱舆t(<10ns)和最低能耗(2.26fJ)。同時,IGZO 2T0C DRAM的高數(shù)據(jù)保持特性使SRAM能夠在長時間斷電(>5000s)后不丟失數(shù)據(jù)以降低待機功耗。

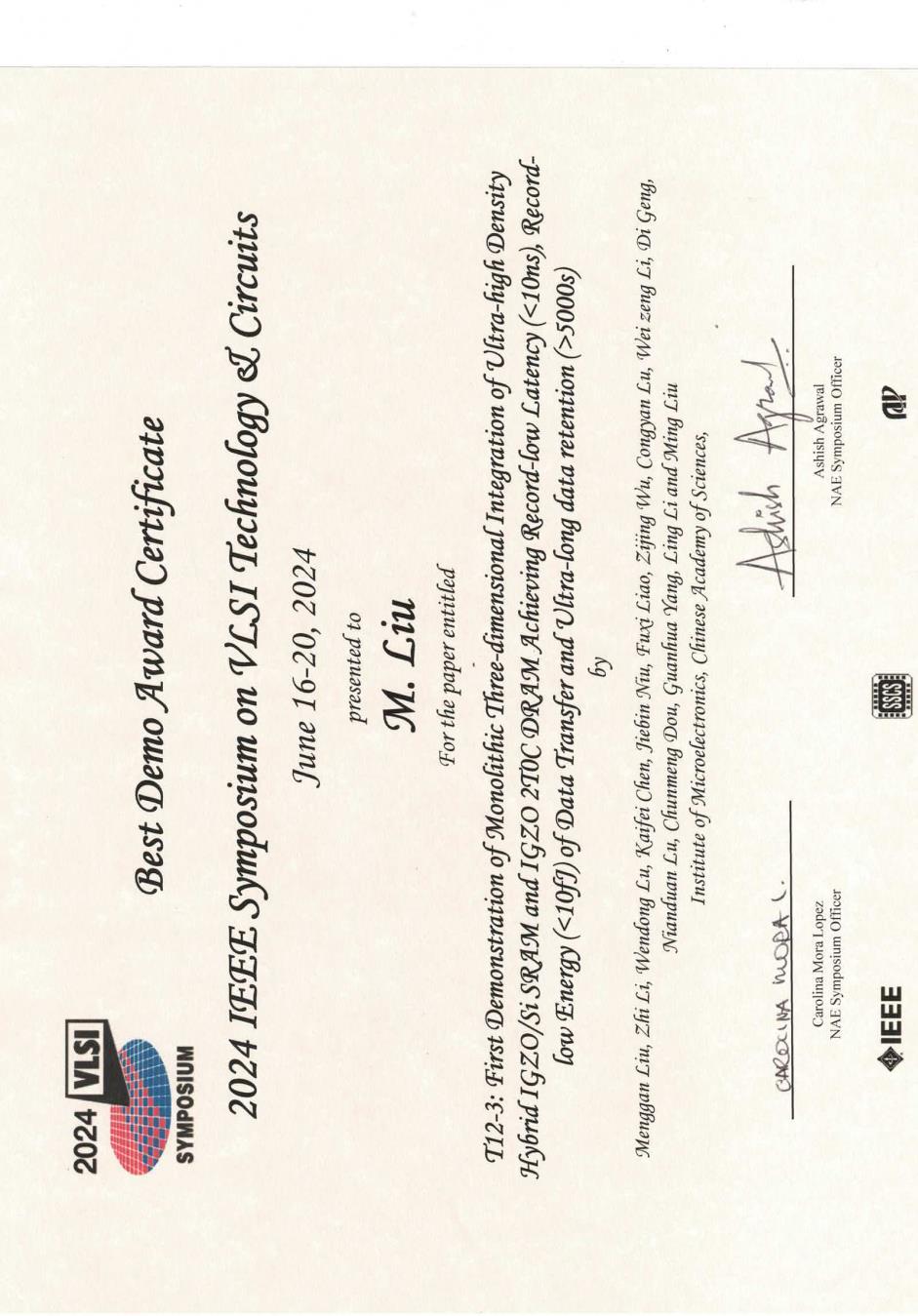

上述研究成果以題為“First Demonstration of Monolithic Three-dimensional Integration of Ultra-high Density Hybrid IGZO/Si SRAM and IGZO 2T0C DRAM Achieving Record-low Latency (<10ns), Record-low Energy (<10fJ) of Data Transfer and Ultra-long data retention (>5000s)”的論文入選2024 VLSI,并獲得大會Best Demo Paper Award獎項。該獎項每年只頒發(fā)2項、分別由工藝與電路分論壇各推選1項,本工作也是大陸首次獲得該獎項。微電子所博士生劉孟淦、李智和盧文棟為共同第一作者,微電子所李泠研究員、楊冠華副研究員以及竇春萌研究員為通訊作者。

圖1?采用三層堆疊的三維集成M3D-SRAM-DRAM結構和對應的電路以及TEM電鏡圖

圖2 混合IGZO/Si 4T SRAM與傳統(tǒng)6T SRAM在面積和能耗上的對比;

M3D-SRAM-DRAM系統(tǒng)與傳統(tǒng)SRAM+DRAM系統(tǒng)在傳輸延時和能耗上的對比

圖3 Best Demo Award獎項

綜合信息