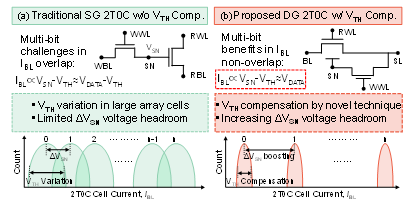

IGZO薄膜晶體管(TFT)由于其極低的關態電流、較高的遷移率和低溫工藝,在新型DRAM的應用中備受關注。與傳統的硅基1T1C DRAM相比,IGZO 2T0C DRAM具有能夠實現多值存儲的優勢,該優勢可提高各個單元的有效存儲密度。但目前基于該方面的研究僅實現了單個存儲單元的多值存儲功能驗證,以及多個單元間SN電壓的均一性,仍需要較為復雜的外圍電路來解決讀取晶體管之間閾值電壓變化的問題。

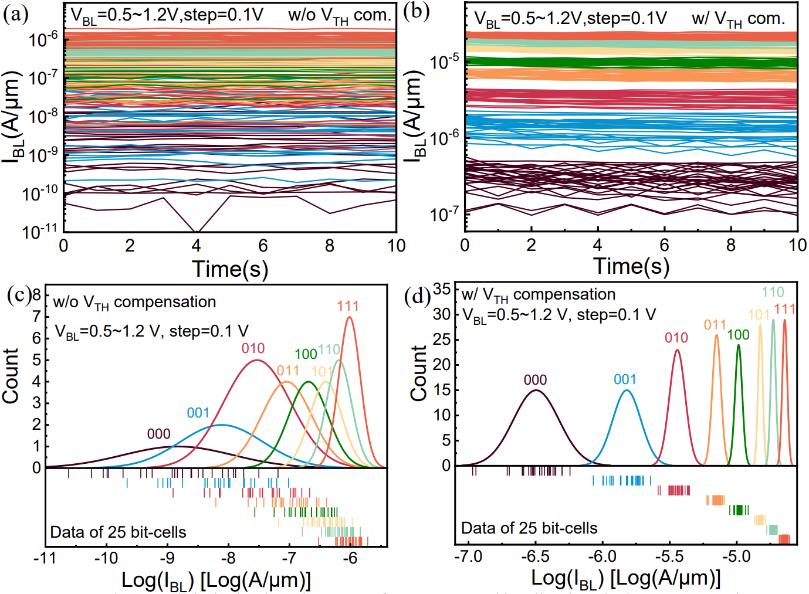

針對上述挑戰,微電子所劉明院士團隊與北京超弦存儲研究院趙超研究員團隊聯合在2023年國際電子器件大會(IEDM)上首次報道了具有單元內閾值電壓補償技術的雙柵IGZO 2T0C DRAM。器件層面上,研究通過控制半導體厚度以及優化金屬半導體接觸,實現了具有正閾值以及高開態電流的雙柵a-IGZO晶體管。電路層面上,提出了一種新型的雙柵2T0C DRAM結構,通過全新的寫入方式,實現了無需外圍電路的存儲單元內閾值電壓補償技術,并且突破了存儲窗口的極限。實驗制備的雙柵2T0C DRAM首次實現了在25個單元間的3-bit存儲功能、目前報道中最大的ΔVSN/ΔVDATA比值(1.46)以及大于1500秒的數據保持時間。

基于該成果的文章“Improved Multi-bit Statistics of Novel Dual-gate IGZO 2T0C DRAM with In-cell VTH Compensation and ΔVSN/ΔVDATA Boosting Technique”入選2023 IEDM。微電子所博士生陳楷飛、超弦存儲研究院朱正勇研究員和微電子所博士生盧文棟為第一作者,微電子所李泠研究員、楊冠華副研究員以及超弦存儲研究院趙超研究員為通訊作者。

圖1:傳統單柵2T0C DRAM在多值存儲中面臨的挑戰以及雙柵2T0C DRAM在實現多值存儲中的優勢

圖2:不具有和具有閾值電壓補償功能的25個雙柵IGZO 2T0C DRAM的讀取電流分布對比

綜合信息