磁隨機存儲器(MRAM)因具有非易失性、低功耗以及高訪問速度等特點,在未來新興存儲領域有著巨大的應用前景。尤其是基于自旋軌道矩(SOT)技術的MRAM存儲器具有超高速、高耐久性的優勢,更適合應用于高速緩存。然而在SOT-MRAM集成中存在幾個關鍵的技術瓶頸,制約了其走向應用。隧道結的刻蝕工藝是其中一個關鍵的技術挑戰和難點。在SOT隧道結(SOT-MTJ)刻蝕過程中,金屬副產物的反濺使得MTJ的MgO隧穿勢壘層(厚度~1 nm)短路,從而造成較低的器件良率。因此,臺灣工研院、臺積電、IMEC、Intel等全世界主要半導體研發機構和企業,都在SOT-MRAM刻蝕工藝上開展了大量工作,提供了良好的解決思路。然而,SOT-MRAM的刻蝕工藝依然是業界面臨的一項重要技術挑戰。

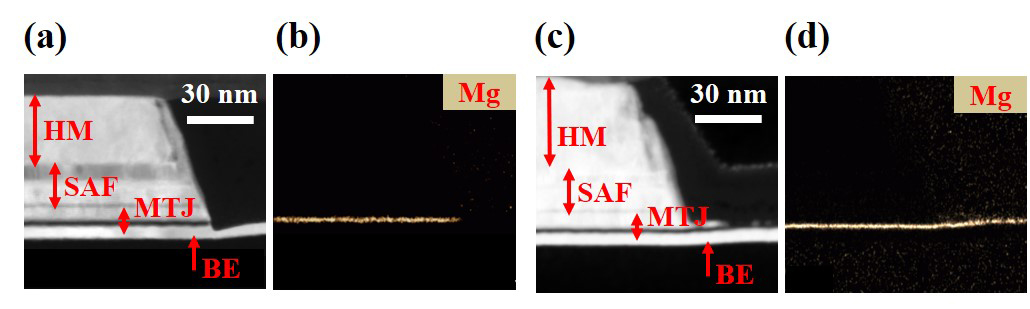

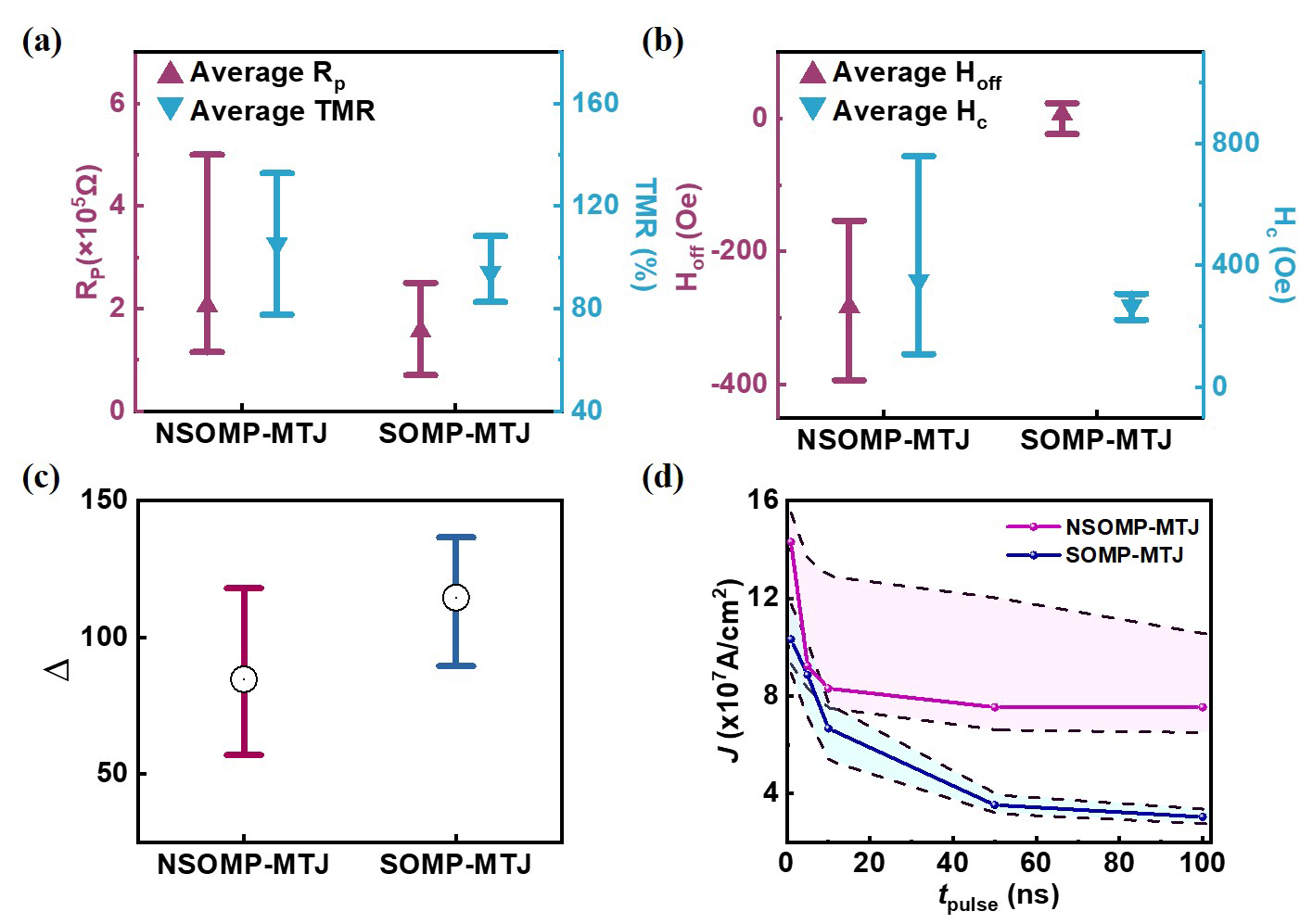

為了更好地解決SOT-MRAM的刻蝕技術難題以實現SOT-MTJ的高密度片上集成,同時研究不同的刻蝕工藝對器件磁電特性的影響,中國科學院微電子研究所集成電路先導工藝研發中心羅軍研究員課題組開發了一種基于垂直磁各向異性SOT-MTJ的刻蝕“停MgO”工藝(SOMP-MTJ),該工藝有效地解決了SOT-MRAM制造中的刻蝕短路問題。傳統的SOT-MTJ刻蝕方法(NSOMP-MTJ)使刻蝕停止在底電極上(圖1a,b),在刻蝕過程中MgO層極易附著金屬,造成器件短路。課題組開發了刻蝕“停MgO”工藝,該工藝使MTJ刻蝕終點精確地停止在~1 nm厚的MgO層上(圖 1c,d)。由于隧穿層MgO的側壁從未暴露,從而避免了MgO層的短路。利用“停MgO”刻蝕工藝制備的SOT-MTJ器件陣列,晶圓的電阻良率可提升至100%,同時還提高了器件的TMR、電阻、矯頑力等關鍵參數的均勻性(圖 2a,b)。另外,“停MgO”器件還具有更高的熱穩定性、更低的翻轉電流密度以及高達1 ns的翻轉速度(圖 2c,d)。該研究成果為高速、低功耗、高集成度SOT-MRAM的刻蝕技術問題提供了關鍵解決方案。

圖1、(a)“停底電極”器件TEM圖,(b)“停底電極”器件EDS圖(c)“停MgO”器件TEM圖,(d)“停MgO”器件EDS圖

圖2、“停底電極”器件(NSOMP-MTJ)和“停MgO”器件(SOMP)磁電特性對比結果。(a)TMR、Rp,(b)偏置場Hoff、矯頑場Hc,(c)熱穩定性因子,(d)翻轉電流密度的性能對比

基于本研究成果的論文“Enhancement of Magnetic and Electric Transport Performance of Perpendicular Spin-Orbit Torque Magnetic Tunnel Junction by Stop-on-MgO Etching Process”近日發表在著名的微電子領域權威期刊《電子器件快報》(IEEE Electron Device Letters,DOI: 10.1109/LED.2023.323683)上。中科院微電子所博士生趙磊為第一作者,中科院微電子所先導中心羅軍研究員和楊美音副研究員為該文的通訊作者。該工作得到了科技部、國家自然科學基金委、中科院和企業有關項目的支持。

論文鏈接:https://ieeexplore.ieee.org/document/10016628

綜合信息