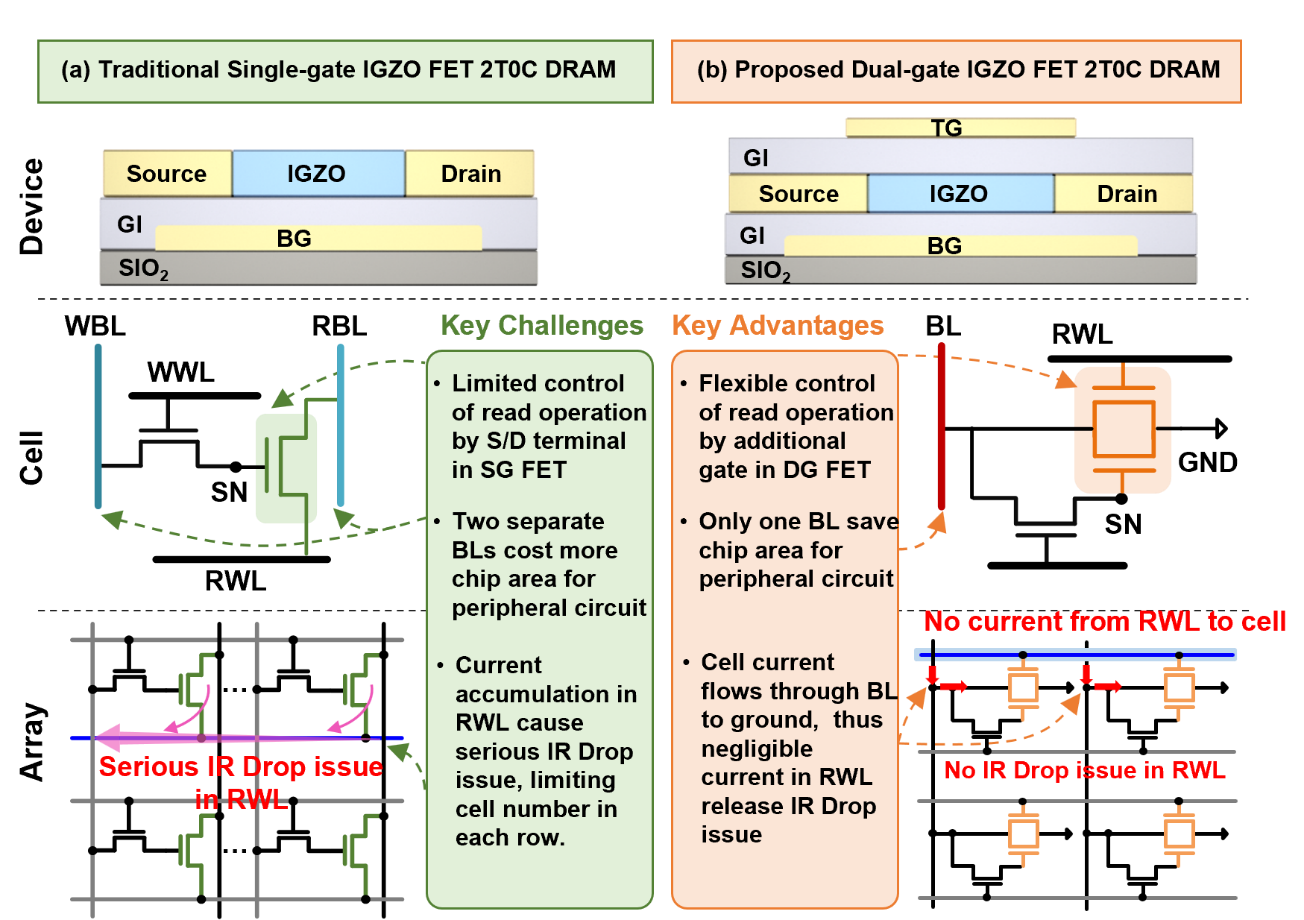

動(dòng)態(tài)隨機(jī)存儲(chǔ)器(DRAM)是存儲(chǔ)器領(lǐng)域中的一個(gè)重要分支。基于銦鎵鋅氧(IGZO)晶體管的2T0C無電容DRAM,有望突破傳統(tǒng)1T1C-DRAM的微縮限制、高刷新率等問題。但相比傳統(tǒng)的1T1C結(jié)構(gòu),2T0C-DRAM仍存在諸多挑戰(zhàn):由于其讀字線與寫字線位于讀晶體管的源漏端,存在潛在的電流分享路徑,不利于讀寫操作;兩條獨(dú)立的讀/寫位線使得電路布局布線更復(fù)雜,需要更復(fù)雜的外圍電路控制讀寫;在陣列級(jí)的DRAM上,讀字線存在嚴(yán)重的IR Drop問題,限制了陣列規(guī)模。

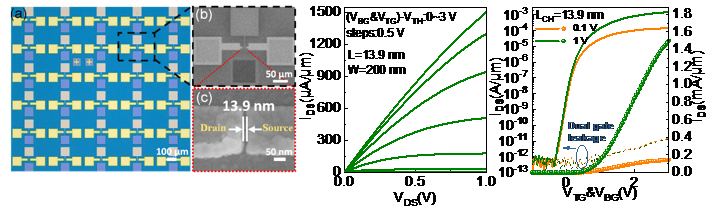

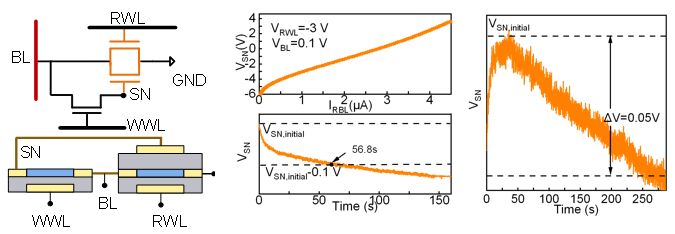

針對(duì)2T0C-DRAM的上述缺陷,微電子所微電子重點(diǎn)實(shí)驗(yàn)室劉明院士團(tuán)隊(duì)與超弦存儲(chǔ)研究院趙超研究員團(tuán)隊(duì)聯(lián)合研發(fā)出基于高性能雙柵IGZO晶體管的新型雙柵結(jié)構(gòu)2T0C-DRAM。器件層面上,通過微縮柵介質(zhì)等效氧化層厚度和半導(dǎo)體厚度來提高器件的柵控能力,并進(jìn)一步優(yōu)化金屬半導(dǎo)體接觸,降低了器件的接觸電阻,實(shí)現(xiàn)了性能優(yōu)異的雙柵a-IGZO短溝道晶體管,其中溝道長(zhǎng)度LCH=13.9 nm,亞閾值擺幅SS=76.8 mV/dec, ION=1500 μA/μm @(VDS=1V,VGS-VTH=3V)。電路層面上,提出了雙柵2T0C-DRAM新結(jié)構(gòu),利用雙柵的兩個(gè)柵端分別完成數(shù)據(jù)存儲(chǔ)和讀寫操作控制,基于柵端控制讀寫的優(yōu)勢(shì),這種雙柵2T0C-DRAM的讀寫更具靈活性、讀字線可免于IR Drop問題、讀寫可共享一條位線。實(shí)驗(yàn)制備的雙柵2T0C-DRAM能夠?qū)崿F(xiàn)大于300 秒的保持時(shí)間、大于100的讀“1”與讀“0”電流開關(guān)比。

基于該成果的文章“First Demonstration of Dual-Gate IGZO 2T0C DRAM with Novel Read Operation, One Bit Line in Single Cell, ION=1500 μA/μm@VDS=1V and Retention Time>300s”入選2022 IEDM,并獲選Top Ranked Students文章。微電子所博士生盧文棟、超弦存儲(chǔ)研究院朱正勇研究員和微電子所博士生陳楷飛為第一作者,微電子所楊冠華副研究員、李泠研究員以及超弦存儲(chǔ)研究院趙超研究員為通訊作者。

圖1單柵與雙柵2T0C-DRAM結(jié)構(gòu)及優(yōu)勢(shì)對(duì)比

圖2短溝道雙柵晶體管光學(xué)顯微圖、SEM圖以及轉(zhuǎn)移輸出曲線

圖3雙柵2T0C-DRAM示意圖以及保持時(shí)間測(cè)試

綜合信息