近日,中科院微電子研究所高頻高壓中心劉新宇研究員團隊與中國科學院蘇州納米所孫錢研究員團隊合作,基于前期在高性能n溝道超薄勢壘增強型HEMT(或n-FETs)研究中積累的研發基礎,結合氮化物特有的極化能帶調控引入AlN極化插入層,獲得了面密度2.1×1013 cm-2的二維空穴氣(2-D Hole Gas,2DHG),為高性能p-FETs乃至GaN基CMOS的研制奠定了材料基礎。同時,團隊通過引入重摻雜p++-GaN蓋帽層初步改善了p-FETs經常存在歐姆接觸勢壘的問題,并基于團隊開發的低損傷p-GaN刻蝕,創新設計出一種階梯式柵槽刻蝕的增強型GaN基p-FET(圖1(a)),克服了由重摻雜p++-GaN層導致的器件擊穿降低的不足。

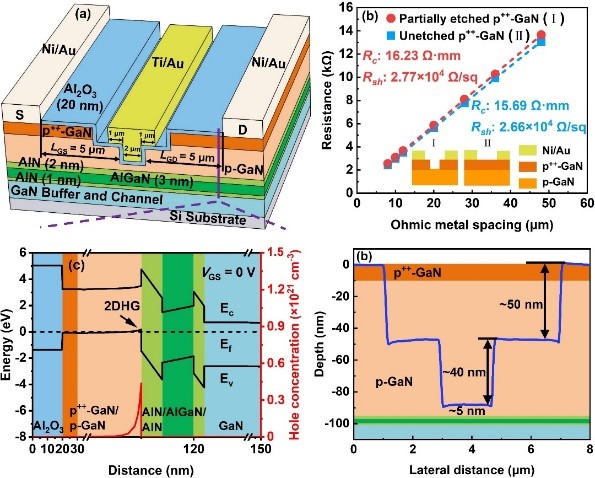

圖1.(a)GaN基p-FETs器件結構圖;(b)刻蝕與未刻蝕歐姆金屬之間p++-GaN的TLM測試結果圖;(c)接觸區能帶圖;(d)AFM測得的柵槽截面圖

GaN材料具有大禁帶寬度(~3.4 eV, Si: ~1.1 eV)、高臨界擊穿電場(~3.3 MV/cm, Si: ~0.3 MV/cm)、高電子漂移飽和速度(~2.5×107 cm/s, Si: ~1×107 cm/s)及高熱導率、高化學穩定性等性能優勢,因此非常適用于高頻、高功率電力電子及射頻器件的制備。目前,基于AlGaN/GaN異質結構的高電子遷移率晶體管(High Electron Mobility Transistors, HEMTs)在手機快充及5G通信領域均已經實現了產業化應用,發揮著不可替代的作用。然而,GaN分立器件的邏輯控制和前級驅動目前大多仍是采用Si基的數字電路,極大的制約了GaN器件高頻應用優勢的發揮,阻礙了GaN器件在芯片電源管理,以及高溫、輻照等極端場景下的應用拓展。互補金屬氧化物半導體(Complementary Metal Oxide Semiconductor, CMOS)由于其突出的靜態功耗優勢,是目前邏輯控制芯片中普遍應用的技術方案,因此基于GaN材料的CMOS技術是推動GaN功率集成電路產業發展至關重要的技術支撐,必將進一步推動GaN功率芯片的智能小型化。

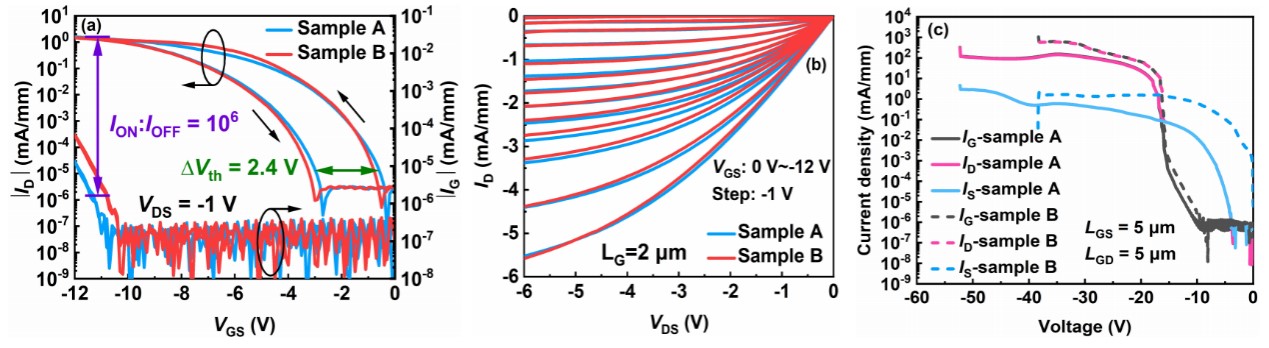

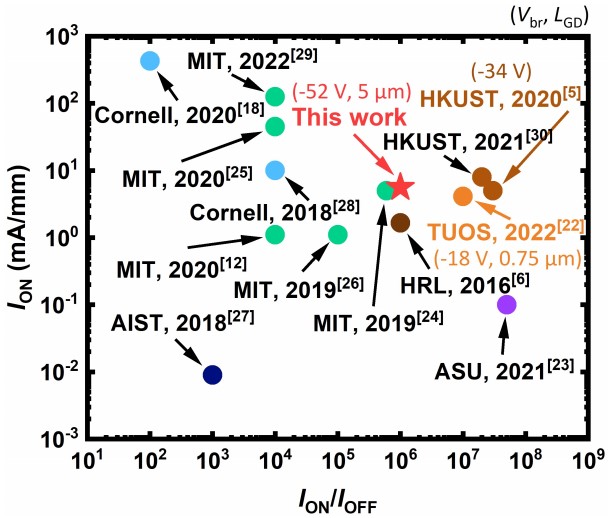

GaN基CMOS技術發展面臨的主要瓶頸之一是高性能p溝道場效應晶體管(p-channel Field Effect Transistors, p-FETs)的研制。本研究發現,外延片表面整體生長的Mg受主重摻雜p++-GaN層可以有效降低歐姆接觸電阻至15.69 Ω·mm(圖1(b)),同時,結合霍爾測試和能帶仿真計算結果證明了在p-GaN/AlGaN之間插入的AlN極化增強層可以有效提升二維空穴氣面密度至2.1×1013 cm-2(圖1(c)),二者對于提升GaN基p-FET的電流能力都有重要的作用。但另一方面,p++-GaN層的引入會使器件的耐壓下降,研究團隊首先基于TCAD仿真計算確定了器件的擊穿主要發生在T型柵靠近漏端的柵帽邊緣處,進而提出了階梯式柵槽刻蝕的技術方案(圖1(d)),通過將柵金屬與p++-GaN層在空間上進行分離,在實現增強型及低歐姆接觸電阻的同時,提高了p-FET的擊穿電壓。本研究制備的GaN基p-FET具有106的高電流開關比、-5.6 mA/mm的電流密度及-52 V的擊穿電壓(圖2),性能指標均處于國際先進水平(圖3)。

圖2. GaN基p-FETs的(a)轉移特性曲線;(b)輸出特性曲線;(c)耐壓測試曲線

圖3. 本研究GaN基p-FETs的電流密度、電流開關比及擊穿電壓與國內外同類型器件對比圖

相關研究成果將于2022年8月以“An Enhancement-mode GaN p-FET with Improved Breakdown Voltage”為題在線發表于IEEE Electron Device Letters期刊(DOI: 10.1109/LED.2022.3184998);其中博士研究生金昊為論文第一作者,黃森和蔣其夢研究員為共同通訊作者。該工作得到了國家重點研發計劃、國家自然科學基金、中國科學院前沿科學重點研究項目以及北京市科委項目等項目的支持。

綜合信息