非晶銦鎵鋅氧化物(a-IGZO)因其具有理想的遷移率、大面積成膜均一、低熱預(yù)算等優(yōu)點,被視為實現(xiàn)高密度三維集成的最佳候選溝道材料之一。三維集成技術(shù)的本質(zhì)是為提高晶體管在芯片上的集成密度。因此,對于兼容后道工藝的a-IGZO晶體管來說,探索其尺寸的極限微縮是實現(xiàn)高密度三維集成的關(guān)鍵。

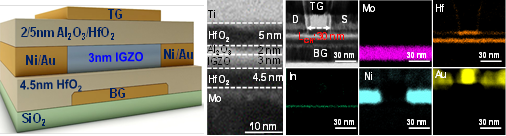

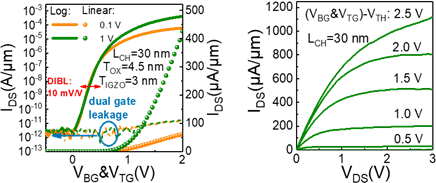

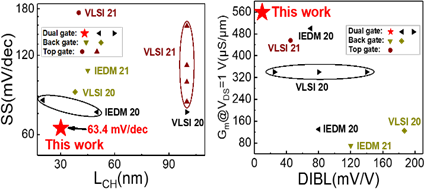

針對上述問題,微電子所重點實驗室科研人員通過采用宏觀電學(xué)測試和微觀表征技術(shù)相結(jié)合的方法,研究了尺寸微縮時a-IGZO晶體管基本特性的變化規(guī)律,通過微縮柵介質(zhì)等效氧化層厚度和半導(dǎo)體厚度來提高器件的柵控能力,進一步優(yōu)化金屬半導(dǎo)體接觸,降低了器件的接觸電阻,并使用柵控能力更強的雙柵互聯(lián)結(jié)構(gòu)與操作模式,實現(xiàn)了性能優(yōu)異的雙柵a-IGZO短溝道晶體管,其中溝道長度LCH=30nm,電容等效厚度CET=0.9 nm,亞閾值擺幅SS=63.4 mV/dec,DIBL=10 mV/V,跨導(dǎo)Gm=559 μS/μm at VDS=1V。

基于該成果的文章“Scaling Dual-Gate Ultra-thin a-IGZO FET to 30 nm Channel Length with Record-high Gm,max of 559 μS/μm at VDS=1 V, Record-low DIBL of 10 mV/V and Nearly Ideal SS of 63 mV/dec”入選2022 VLSI,同時入選demon session 文章。微電子所碩士生陳楷飛為第一作者,楊冠華副研究員和李泠研究員為通訊作者。

圖1. 器件結(jié)構(gòu)示意圖及TEM表征圖

圖2. 雙柵IGZO晶體管轉(zhuǎn)移曲線及輸出曲線

圖3. 該工作與近兩年短溝道氧化物晶體管性能對比

綜合信息