基于憶阻器的儲(chǔ)備池計(jì)算(Reservoir Computing, RC)作為一種處理時(shí)間序列信息的輕量化網(wǎng)絡(luò)近幾年受到了廣泛的關(guān)注。但物聯(lián)網(wǎng)快速發(fā)展對(duì)計(jì)算網(wǎng)絡(luò)的高密度和低功耗提出了更高要求。

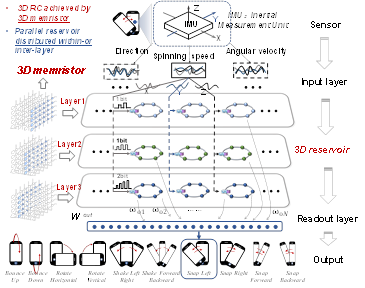

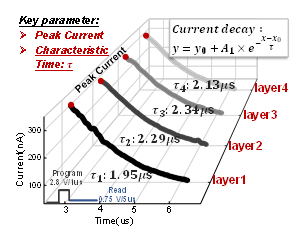

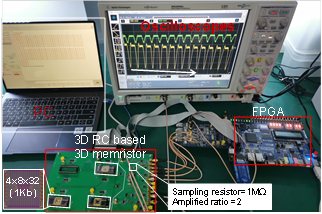

針對(duì)上述問(wèn)題,微電子所重點(diǎn)實(shí)驗(yàn)室科研人員首次基于三維憶阻器陣列搭建了三維深度儲(chǔ)備池網(wǎng)絡(luò)。在器件層面,通過(guò)并行的器件結(jié)構(gòu)設(shè)計(jì),降低了器件循環(huán)與循環(huán)之間的差異,有效的降低了系統(tǒng)本身的噪聲;在軟件層面,通過(guò)對(duì)輸入策略的設(shè)計(jì),與三維憶阻器架構(gòu)的結(jié)合,提高了器件與器件之間的差異性,使得儲(chǔ)層內(nèi)部狀態(tài)更加豐富。通過(guò)軟硬件協(xié)同優(yōu)化,成功的實(shí)現(xiàn)了手機(jī)動(dòng)態(tài)手勢(shì)識(shí)別的任務(wù),并在板卡系統(tǒng)上得以驗(yàn)證。三維儲(chǔ)備池計(jì)算系統(tǒng)表現(xiàn)出了高準(zhǔn)確率(90%)、高面積效率(5.12 TOPS/mm2)和低功耗(0.78 pJ/operation)。

基于該成果的文章“3D Reservoir Computing with High Area Efficiency (5.12 TOPS/mm2) Implemented by 3D Dynamic Memristor Array for Temporal Signal Processing”入選2022 VLSI。微電子所博士生孫文絢為第一作者,許曉欣副研究員和尚大山研究員為通訊作者。

圖1. 三維儲(chǔ)備池系統(tǒng)實(shí)現(xiàn)動(dòng)態(tài)手勢(shì)識(shí)別示意圖

圖2. 三維憶阻器動(dòng)態(tài)特性

圖3. 板卡功能驗(yàn)證

綜合信息