近日微電子所在新型存儲(chǔ)器及硬件安全芯片研究領(lǐng)域取得重要進(jìn)展。劉明院士科研團(tuán)隊(duì)兩篇研究論文成功入選2020年第40屆超大規(guī)模集成電路研討會(huì)(Symposium on VLSI)。

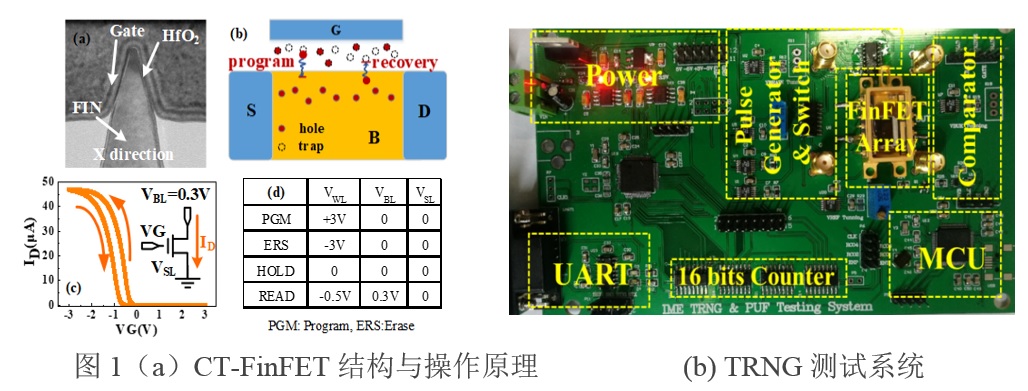

在硬件安全芯片領(lǐng)域,劉明院士/呂杭炳研究員團(tuán)隊(duì)展示了一種利用電荷俘獲鰭式晶體管(Charge Trapping FinFET,CT-FinFET)器件短期閾值電壓恢復(fù)特征的真隨機(jī)數(shù)發(fā)生器(TRNG)芯片(圖1)。研究人員創(chuàng)新地設(shè)計(jì)了一種時(shí)間-頻率轉(zhuǎn)換電路,將CT-FinFET閾值電壓的弛豫時(shí)間轉(zhuǎn)變?yōu)楦咚僬骐S機(jī)數(shù)據(jù)流。該TRNG在-10~85℃范圍,對(duì)幅度高達(dá)600mV和頻率高達(dá)1.5G Hz的功率噪聲表現(xiàn)出極大的抗攻擊能力。論文展示的TRNG芯片通過了NIST 800-22和NIST 800-90B所有的隨機(jī)性測(cè)試項(xiàng),是一種非常有潛力面向先進(jìn)工藝節(jié)點(diǎn)的硬件安全解決方案。該項(xiàng)工作被組委會(huì)邀請(qǐng)參加今年VLSI Demo Session的展示。

上述研究成果以題為“Robust True Random Number Generator Using Stochastic Short-Term Recovery of Charge Trapping FinFET for Advanced Hardware Security”的論文入選2020 VLSI Technology。微電子所楊建國(guó)副研究員和丁慶婷博士為共同第一作者,呂杭炳研究員和劉明院士為通訊作者。

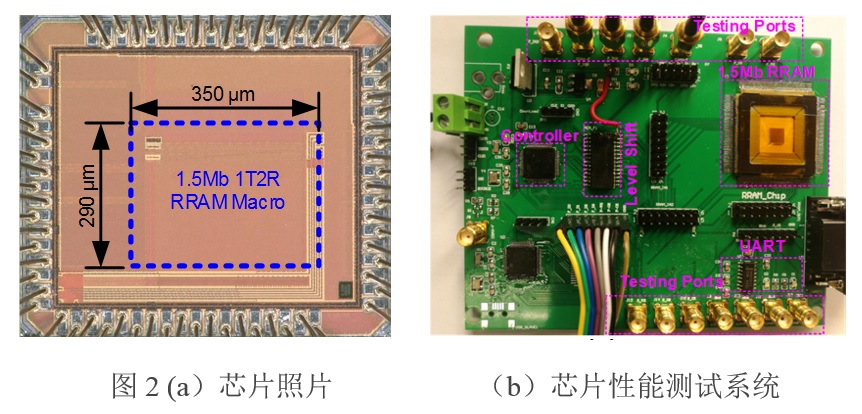

在新型存儲(chǔ)器方面,劉明院士/呂杭炳研究員團(tuán)隊(duì)與復(fù)旦大學(xué)薛曉勇副教授合作首次提出了基于PMOS選擇器的1T2R 結(jié)構(gòu)RRAM單元,并采用分層位線和三態(tài)單元存儲(chǔ)技術(shù),使漏電流降低了90%以上。設(shè)計(jì)了電流精確補(bǔ)償限流電路和自適應(yīng)寫驅(qū)動(dòng)電路,大幅度提高了陣列的可靠性,同時(shí)開發(fā)了基于1T2R 自身陣列特點(diǎn)的高速電流型讀取電路,實(shí)現(xiàn)了極端條件下的高速讀取。論文展示了28nm的1.5Mb RRAM測(cè)試芯片,將嵌入式NVM 存儲(chǔ)密度記錄提高了40%,達(dá)到14.8 Mb / mm2(圖2)。

上述研究成果以題為“A 28nm 1.5Mb Embedded 1T2R RRAM with 14.8 Mb/mm2 Using Sneaking Current Suppression and Compensation Techniques”的論文入選2020 VLSI Circuit。微電子所楊建國(guó)副研究員為第一作者,呂杭炳研究員和復(fù)旦大學(xué)薛曉勇副教授為通訊作者。

劉明院士團(tuán)隊(duì)在RRAM方向的研究工作始于2005年,在基礎(chǔ)物理、器件結(jié)構(gòu)、電路設(shè)計(jì)等方向進(jìn)行了系統(tǒng)深入的研究。研究團(tuán)隊(duì)于2015年開始先后與國(guó)內(nèi)主要代工廠中芯國(guó)際、華力微電子及上海集成電路研發(fā)中心合作開發(fā)嵌入式RRAM的量產(chǎn)技術(shù),在中芯國(guó)際28nm工藝平臺(tái)、華力40nm工藝平臺(tái)上開發(fā)了成套RRAM單元結(jié)構(gòu)與集成技術(shù),為在先進(jìn)工藝節(jié)點(diǎn)上設(shè)計(jì)新一代低功耗、高性能SOC芯片提供了重要的技術(shù)平臺(tái),相關(guān)成果已經(jīng)開始和終端企業(yè)合作推進(jìn)產(chǎn)業(yè)化。在RRAM高密度三維集成方面,劉明院士團(tuán)隊(duì)提出了可與3D NAND相媲美的垂直三維集成架構(gòu),在國(guó)際上率先成功研制了4層(2015年 IEDM)與8層(2017年 IEDM)RRAM三維堆疊陣列,相關(guān)研究工作被國(guó)際同行列為近五十年來RRAM發(fā)展歷史中重要事件之一。

相關(guān)工作得到國(guó)家自然基金委、科技部重點(diǎn)研發(fā)計(jì)劃、中國(guó)科學(xué)院B類先導(dǎo)專項(xiàng)等項(xiàng)目的支持。

背景介紹:

VLSI與ISSCC(國(guó)際固態(tài)電路會(huì)議)、IEDM(國(guó)際電子器件會(huì)議)并稱微電子技術(shù)領(lǐng)域的“奧林匹克盛會(huì)”,VLSI是超大規(guī)模集成電路和半導(dǎo)體器件領(lǐng)域里最頂尖的國(guó)際會(huì)議之一,是展現(xiàn)IC技術(shù)最新成果的重要窗口。據(jù)組委會(huì)介紹,今年VLSI收到了創(chuàng)紀(jì)錄數(shù)量的投稿,而論文錄用率創(chuàng)歷史新低。器件與工藝方向,微電子所作為大陸唯一論文入選單位;電路設(shè)計(jì)方向,大陸也僅有兩篇論文入選(另外一篇為浙江大學(xué)與德克薩斯大學(xué)奧斯汀分校合作論文),這也是微電子所電路工作的首次入選。

相關(guān)鏈接:https://vlsisymposium.org

綜合信息