近日,微電子所集成電路先導工藝研發(fā)中心在下一代新型FinFET邏輯器件工藝研究上取得重要進展。

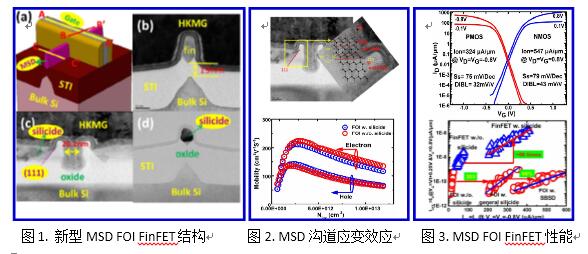

隨著主流FinFET器件工藝的持續(xù)微縮,其在柵控與性能提升上面臨越來越大的技術挑戰(zhàn)。微電子所殷華湘研究員的課題組相繼提出S-FinFET、后柵納米線及體硅絕緣Fin-on-insulator(FOI)FinFET等創(chuàng)新技術(圖1-3),探索采用新型器件結(jié)構(gòu)來突破未來主流集成電路工藝微縮限制的可能技術方法。然而這些新器件結(jié)構(gòu)雖然柵控更為優(yōu)秀卻面臨性能不足,弱于主流FinFET工藝的巨大挑戰(zhàn)。針對這些挑戰(zhàn),研究小組利用低溫低阻NiPt硅化物在新型FOI FinFET上實現(xiàn)了全金屬化源漏(MSD),顯著降低源漏寄生電阻,從而將N/PMOS器件性能提高大約30倍,使得驅(qū)動性能達到了國際先進水平。基于本研究成果的論文“FOI FinFET with Ultra-low Parasitic Resistance Enabled by Fully Metallic Source and Drain Formation on Isolated Bulk-fin”(通訊作者:殷華湘、張青竹,Session 17.3)被2016年IEEE國際電子器件大會(IEDM)接收,并在IEDM的關鍵分會場之一——硅基先導CMOS 工藝和制造技術(PMT)上由第一作者張青竹作了學術報告。約700名來自全球集成電路邏輯器件與工藝技術領域的知名專家聆聽了該報告,報告內(nèi)容得到IBM、意法半導體和海思半導體等國際知名主流集成電路公司的熱切關注,并在會后進行了充分的交流。該技術成果同時得到IBM公司主管先進集成電路技術研發(fā)的經(jīng)理H. Bu的高度評價和充分的認可,意法半導體的高級技術專家P. Morin也高度贊揚該文所提出的技術方案。

當前主流FinFET(Tri-gate)器件工藝是16/14nm以及10nm節(jié)點集成電路制造的關鍵技術。預計在7-5nm及以下技術代漏電流控制和源漏寄生電阻問題面臨嚴重的技術挑戰(zhàn)。SOI器件具有天然的介質(zhì)隔離,漏電流和寄生電容更小、速度快,但是面臨高昂的襯底成本和驅(qū)動性能差等難題。兼容主流體硅FinFET工藝,通過體硅襯底形成介質(zhì)隔離的類SOI器件,即FOI FinFET已經(jīng)成為重要的研究方向,但是該類器件由于介質(zhì)隔離的硅fin更小,源漏寄生電阻已經(jīng)成為限制其驅(qū)動性能最大的制約因素。采用基于低溫低阻NiPt硅化物的全金屬化源漏在介質(zhì)隔離上可以有效消除常規(guī)體fin上的漏電影響,并大幅降低源漏寄生電阻,使實際物理柵長為20nm的FOI FinFET的源漏接觸電阻和方塊電阻分別減小10倍和1.1倍,從而將N/P型FOI FinFET器件性能提高大約30倍,并且維持新結(jié)構(gòu)的優(yōu)異短溝道抑制特性。此外,由NiPt全金屬源漏與Si界面的晶格失配在溝道中產(chǎn)生了附加張應力,有效地增強了電子遷移率,為N型 FOI FinFET的溝道遷移率增強技術提供新的集成方案。同時通過肖特基源漏(SBSD)技術使源漏寄生電阻進一步降低,有效地提升了P型 FOI FinFET器件驅(qū)動性能(大于50%)。研究結(jié)果表明,全金屬化源漏FOI FinFET相比類似工藝的常規(guī)FinFET漏電降低1個數(shù)量級,驅(qū)動電流增大2倍,驅(qū)動性能在低電源電壓下達到國際先進水平。由于替代了傳統(tǒng)的源漏SiGe外延技術,與極小pitch的大規(guī)模FinFET器件的兼容性更好,有助于降低制造成本,提高良品率,具有很高的技術價值。

綜合信息