近日,微電子所微電子器件與集成技術重點實驗室劉明院士團隊在阻變存儲器(RRAM)高密度集成方面取得突破性進展,提出了一種與CMOS工藝完全兼容,具有高均一性的高性能選通器件,為兩端結構電阻型存儲器的高密度三維集成提供了解決方案。基于本研究成果的論文“Fully BEOL Compatible TaOx-based Selector with High Uniformity and Robust Performance”(通訊作者:呂杭炳、劉明)被2016年IEEE國際電子器件大會(IEDM)接收,第一作者羅慶在大會上作了報告。

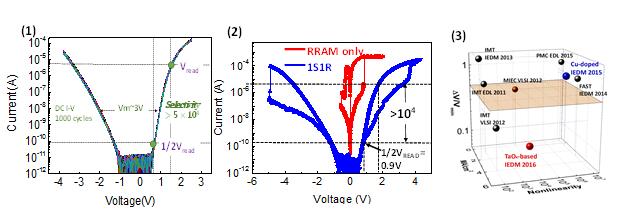

交叉陣列中的漏電流問題是存儲器高密度集成的主要障礙。在1T1R結構中,晶體管作為選通管隔絕了旁路漏電,但晶體管不適用于三維堆疊。因此,開發(fā)具有高均一性、高選擇比、高電流密度、可三維堆疊的選通器件是實現(xiàn)RRAM的三維集成的關鍵。現(xiàn)有的選通管器件很難同時滿足上述幾個要求。針對該問題,劉明團隊提出了利用梯形能帶結構的構建選通管器件的思路,開發(fā)了一種具有高度均一性,同時具有較高選擇比和電流密度的選通器件,其漏電流<10 pA,非線性比>50000,開態(tài)電流密度>1MA/cm2以及超高耐久性(>1010)。

IEEE國際電子器件大會始創(chuàng)于1954年,是報道半導體及電子領域最新的科技、研發(fā)設計、制造、物理學及建模技術的主要論壇,為產(chǎn)學研界的研究學者提供關于電子器件最新研究進展和研究成果的國際交流平臺。

(1)高均一性高選擇比的選擇器的典型I-V特性。(2)1RRRAM和集成選通器1S1R結構的I-V特性。(3)各類選通管器件性能參數(shù)對比。

綜合信息