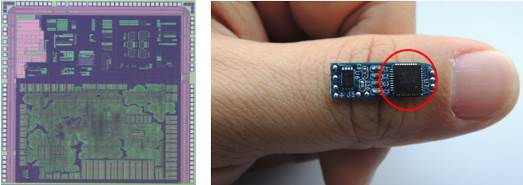

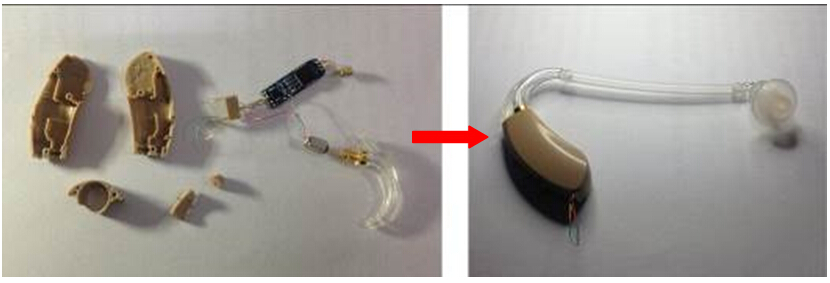

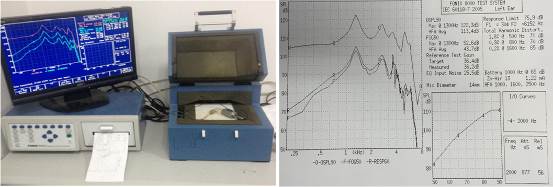

該SoC芯片采用單芯片全集成解決方案(架構如圖1所示,助聽器芯片、硬件系統及樣機分別如圖2、圖3所示),芯片集成片上電源LDO、時鐘振蕩器RC、低噪聲模擬前端AFE、低功耗數字信號處理器DSP和高精度音頻輸出DAC。其中,低噪聲AFE包含自適應預放大電路PGA和低噪聲16-bit ADC,低功耗DSP包括專用指令集處理器ASIP和若干協處理器。助聽器SoC電源電壓1V,時鐘頻率8MHZ,整機工作電流為1.2mA。基于該SoC芯片的助聽器樣機電聲測試結果如圖4所示,其中飽和輸出達到122.3dB,最大增益52.6dB,等效輸入噪聲25.5dB,諧波失真0.2%@1600Hz,整機功耗1.22mW。基于該SoC芯片,只需配備麥克風、喇叭、EEPROM、鋅空電池和少量電容,即可搭建典型助聽器系統,也可以通過編程,應用于聲音采集、語音降噪等其他領域。

目前,該SoC芯片現已通過助聽器行業標準測試,各項性能、功耗指標滿足國際中端助聽器產品需求。項目組正與企業展開深度合作,進行小批量助聽器樣機生產,推動我國助聽器產業從制造到創新的跨越發展。

圖1.低功耗助聽器SoC及系統框圖

圖2.助聽器SoC裸片、QFN40L芯片及硬件系統

圖3.助聽器樣機

圖4.助聽器樣機測試環境及測試結果

綜合信息