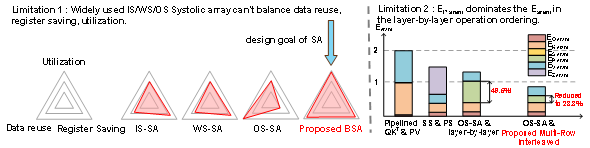

基于Transformer神經(jīng)網(wǎng)絡(luò)的大模型(BERT、GPT等)的廣泛應(yīng)用,讓機器具備了更接近人類的理解和表達能力,體現(xiàn)了人工智能在提高生產(chǎn)力上的巨大潛力。注意力機制在Transformer的計算能耗和延遲中起重要作用,針對注意力機制設(shè)計高能效和高速的加速器具有較高的研究意義。但現(xiàn)有注意力加速器的硬件架構(gòu)中存在兩個主要局限性,首先,常用的輸入固定、權(quán)重固定以及輸出固定的脈動陣列架構(gòu)無法在數(shù)據(jù)復用、寄存器使用和利用率之間取得平衡;其次,逐層計算的操作順序?qū)е轮虚g結(jié)果的 SRAM 訪問開銷過高。這些局限阻礙了加速器能效和速度進一步提升。

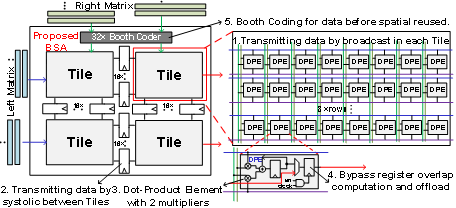

為應(yīng)對上述挑戰(zhàn),中國科學院微電子研究所集成電路制造技術(shù)全國重點實驗室科研團隊設(shè)計了一種高能效、高利用率注意力加速器硬件架構(gòu)。該架構(gòu)采用內(nèi)外積混合的 “平衡脈動陣列”(Balanced Systolic Array)結(jié)構(gòu)。團隊基于數(shù)據(jù)復用理論公式指導,確定最佳的內(nèi)外積混合陣列形狀,其能效相比傳統(tǒng)脈動陣列提升了40%,利用率達99.5%。在操作流程上,團隊提出了“多行交織”(Multi-Row Interleaved)的操作順序,使 SRAM 能耗降低了 31.7%。基于上述兩種技術(shù),團隊設(shè)計的注意力加速器在能效方面提升了39%,在吞吐量×能效方面較現(xiàn)有工作提升了38%。

此項研究成果以“An Energy-Efficient High-Utilization Hardware Architecture for Attention Mechanism in Transformer using Balanced Systolic Array and Multi-Row Interleaved Operation Ordering”為題在第62屆國際設(shè)計自動化會議(DAC)上進行了口頭報告。碩士研究生周海洋為第一作者,呼紅陽助理研究員為通訊作者。

該工作獲得了國家自然科學基金青年基金項目和基礎(chǔ)科學中心項目的資助。

、

、

圖1.?傳統(tǒng)注意力加速器的局限性

圖2. 提出的平衡脈動陣列結(jié)構(gòu)

科研工作