邊緣端人工智能(AI)硬件憑借其低延遲、高能效和強(qiáng)隱私性等優(yōu)勢(shì),得到廣泛關(guān)注與應(yīng)用。在功耗嚴(yán)格受限的邊緣端部署AI硬件,不僅需要高能效以滿足功耗約束,還需要高并行度以提升實(shí)時(shí)性能。基于阻變存儲(chǔ)器(RRAM)的存算一體和近閾值計(jì)算作為兩種高效能計(jì)算范式,有望在實(shí)現(xiàn)高能效、高并行的AI硬件中發(fā)揮關(guān)鍵作用。然而,受工藝波動(dòng)的影響,這兩種計(jì)算范式的規(guī)模與可擴(kuò)展性仍面臨挑戰(zhàn)。此外,如何有效結(jié)合這兩種范式以開(kāi)發(fā)低功耗、高并行的AI硬件,目前仍缺乏深入研究。

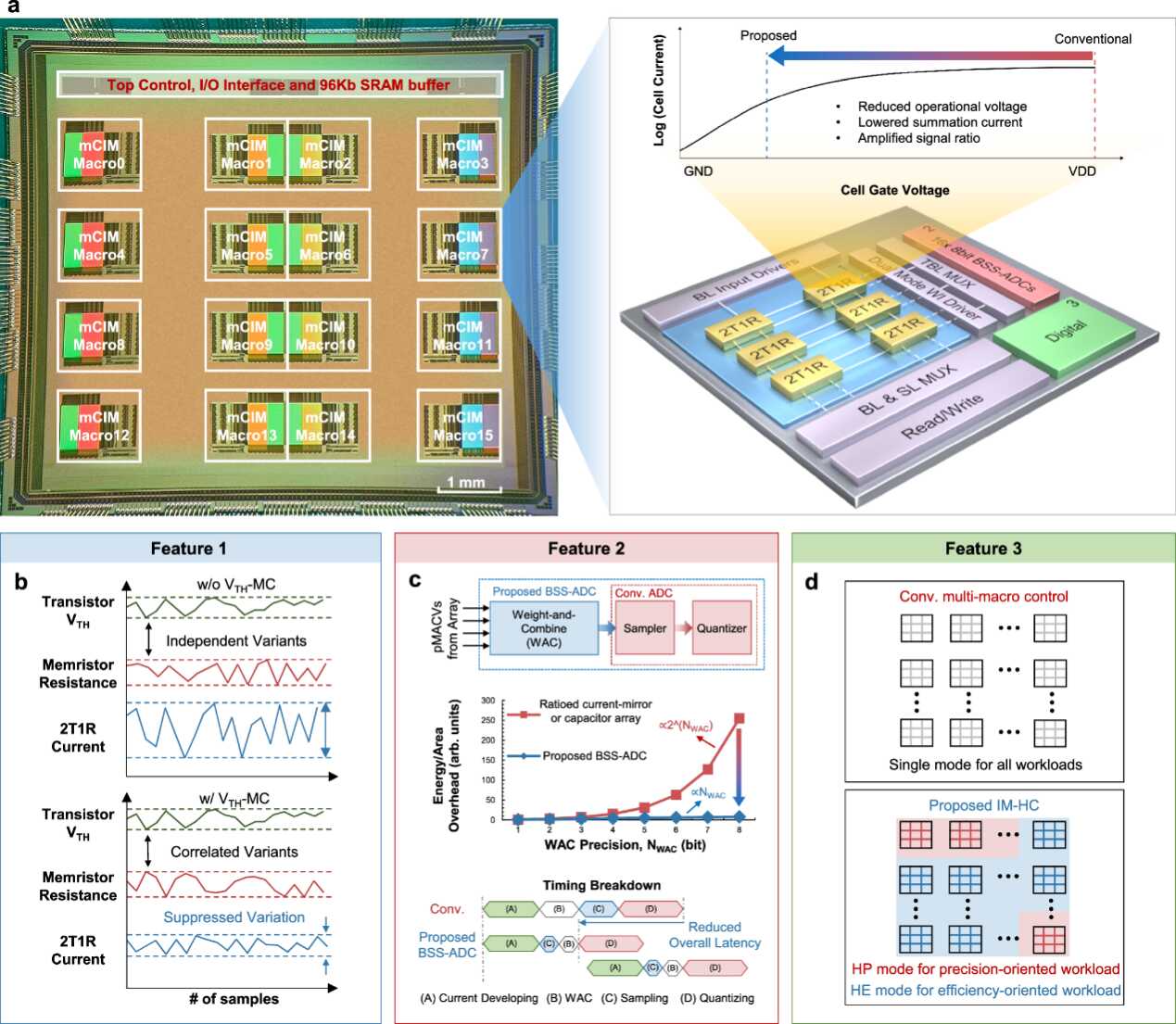

針對(duì)上述挑戰(zhàn),中國(guó)科學(xué)院微電子研究所集成電路制造技術(shù)全國(guó)重點(diǎn)實(shí)驗(yàn)室科研團(tuán)隊(duì)設(shè)計(jì)并實(shí)現(xiàn)了一款基于近閾值計(jì)算的RRAM存算一體芯片。團(tuán)隊(duì)利用雙晶體管單阻變存儲(chǔ)器(2T1R)單元,將RRAM的阻變特性轉(zhuǎn)化為閾值電壓調(diào)控特性,提出RRAM-CMOS閾值電壓失配抵消技術(shù),有效抑制了長(zhǎng)期困擾兩種計(jì)算范式的工藝波動(dòng)問(wèn)題。針對(duì)網(wǎng)絡(luò)模型多比特乘累加運(yùn)算的需求,團(tuán)隊(duì)提出了基于電荷堆疊的新型電荷域計(jì)算技術(shù),實(shí)現(xiàn)了一種采樣、加權(quán)與量化一體化模數(shù)轉(zhuǎn)換電路,顯著降低了外圍電路的功耗與面積開(kāi)銷。團(tuán)隊(duì)在多核存算一體系統(tǒng)中引入了核間混合精度控制技術(shù),通過(guò)對(duì)神經(jīng)網(wǎng)絡(luò)各層數(shù)據(jù)特征進(jìn)行分析,為每個(gè)計(jì)算核心配置優(yōu)化的累加與量化方法,實(shí)現(xiàn)了任務(wù)級(jí)推理功耗的高效優(yōu)化。

基于上述設(shè)計(jì),團(tuán)隊(duì)成功流片驗(yàn)證了具有16個(gè)計(jì)算核心的近閾值RRAM存算一體芯片。該芯片可實(shí)現(xiàn)256通道累加的高并行模擬計(jì)算,平均相對(duì)標(biāo)準(zhǔn)差低至2.4%,計(jì)算能效可達(dá)55.21至88.51 TOPS/W。本研究展示了高能效、高并行近閾值RRAM存算一體技術(shù),為邊緣AI硬件的發(fā)展提供了新思路。

本研究以"A near-threshold memristive computing-in-memory engine for edge intelligence"為題發(fā)表在《Nature Communications》期刊(論文鏈接:https://www.nature.com/articles/s41467-025-61025-4)。微電子所博士畢業(yè)生王琳方博士,微電子所博士研究生李偉增及周治道為共同第一作者,微電子所竇春萌研究員為通訊作者。該研究得到了復(fù)旦大學(xué)、中國(guó)科學(xué)院計(jì)算技術(shù)研究所、中國(guó)科學(xué)院軟件研究所等多個(gè)合作單位的大力支持與協(xié)作。

?圖1. (a)芯片顯微照片、關(guān)鍵結(jié)構(gòu)和近閾值計(jì)算方案;(b)RRAM-CMOS閾值電壓失配抵消技術(shù);(c)采樣、加權(quán)與量化一體化模數(shù)轉(zhuǎn)換技術(shù);(d)核間混合精度控制技術(shù)。

科研工作