物聯(lián)網(wǎng)與人工智能技術(shù)的迅猛發(fā)展對邊緣節(jié)點計算平臺的實時數(shù)據(jù)處理能力與能效提出了更高要求。基于新型存儲器的非易失存內(nèi)計算技術(shù)可實現(xiàn)數(shù)據(jù)的原位存儲與計算、將數(shù)據(jù)搬運帶來的功耗與延遲開銷最小化,從而大幅提升邊緣設(shè)備的數(shù)據(jù)處理能力與效能比。但由于基礎(chǔ)單元特性的非理想因素,陣列中的寄生效應(yīng)以及模數(shù)轉(zhuǎn)換電路的硬件開銷,非易失存內(nèi)計算仍面臨計算性能與能效方面的限制。

圍繞上述關(guān)鍵問題,微電子所劉明院士團隊采用跨層次協(xié)同設(shè)計的方法,提出了高并行與高效能比的新型RRAM存內(nèi)計算結(jié)構(gòu)。

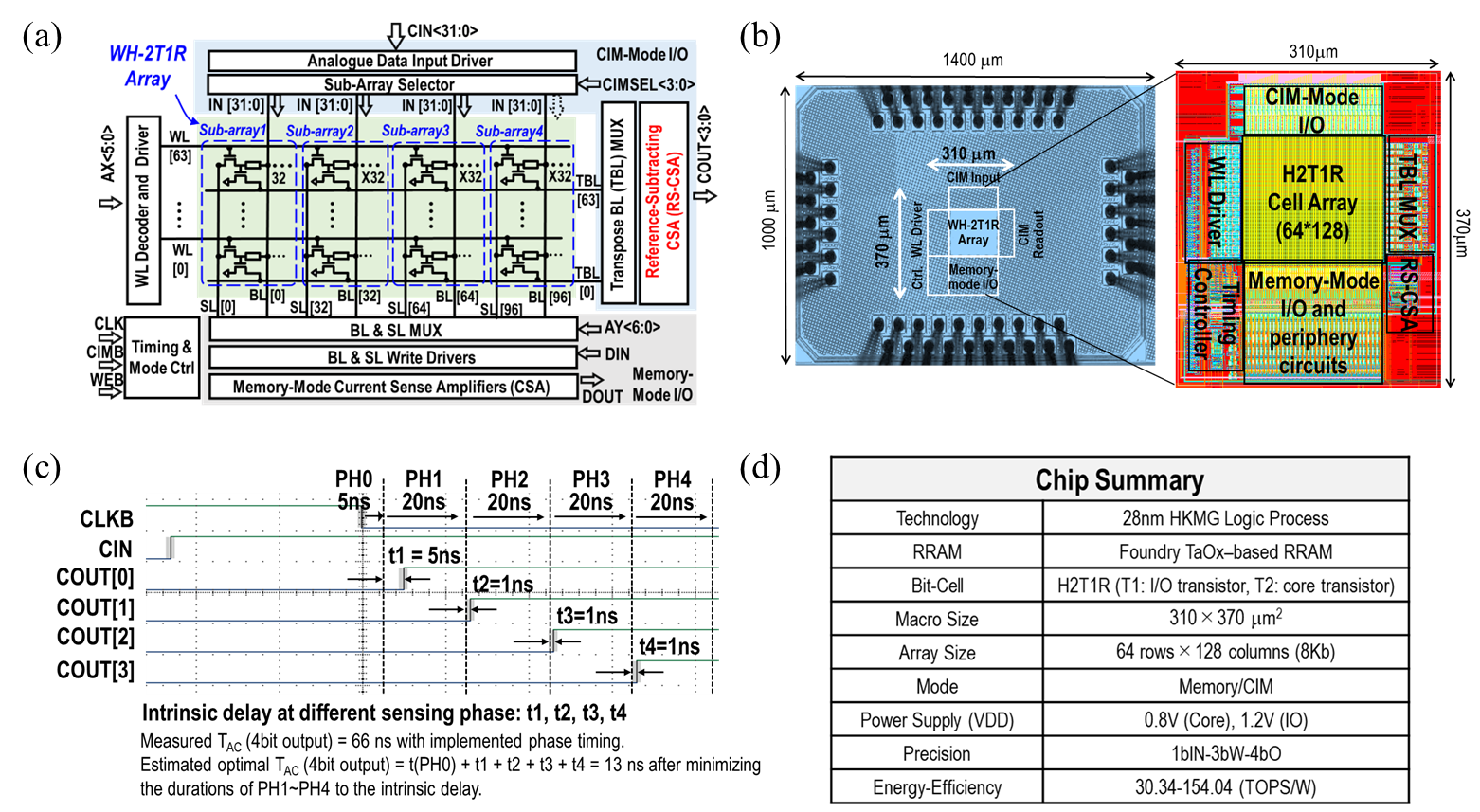

在器件層面,研究團隊提出了帶權(quán)重二晶體管一憶阻器(WH-2T1R)的存算陣列結(jié)構(gòu)。WH-2T1R結(jié)構(gòu)使用core晶體管構(gòu)成解耦的存算數(shù)據(jù)通路來減小寄生效應(yīng)對計算電流的影響,相較1T1R結(jié)構(gòu)只額外造成30.3%的面積開銷。計算單元利用第二晶體管亞閾值區(qū)放大特性提高計算13.5倍開關(guān)比的同時降低88%的低阻態(tài)計算電流,從而實現(xiàn)了63.4%的乘加操作功耗降低。得益于計算開關(guān)比的提升,該RRAM存內(nèi)計算結(jié)構(gòu)可支持更高的輸入并行度和多比特乘加操作。

在電路層面,研究團隊提出了參考電流減式電流型靈敏放大器的讀出電路。由參考電流減支路根據(jù)上一次讀出結(jié)果先對輸入電流進行電流減再送到電流鏡讀出數(shù)據(jù)。參考電流減支路對半減小了電流鏡輸入電流范圍,使RRAM存算結(jié)構(gòu)支持的計算電流范圍倍增,能實現(xiàn)更高輸入并行和多比特乘加,并取得79.5%的讀出電路功耗降低。研究團隊通過進一步優(yōu)化電流型靈敏放大器電流減配置,實現(xiàn)積分非線性誤差5倍提升,微分非線性誤差3.75倍提升。

在算法映射層面,研究團隊提出了高位數(shù)據(jù)冗余(MSB_RSM)的映射策略。RRAM存內(nèi)計算結(jié)構(gòu)配備有不同第二晶體管multiplier參數(shù)的多組陣列和額外的一組冗余陣列。其中不同第二晶體管用于映射多比特權(quán)值的不同比特位。由于RRAM和晶體管非理想因素對計算電流的影響不容忽視,冗余陣列用于額外映射權(quán)值對非理想因素補償。經(jīng)過對不同比特位補償效果的分析,MSB-RSM對高位權(quán)值進行操作時能減小1σ誤差40%。得益于更穩(wěn)定的計算電流,在ResNet-18模型下的CIFAR-10和CIFAR-100任務(wù)獲得了0.96%和2.83%的準確度提升。

上述方案在團隊自主開發(fā)的嵌入式28nm 工藝上得到驗證,新型RRAM存內(nèi)計算結(jié)構(gòu)支持高并行的模擬域乘加操作,在1比特輸入、3比特權(quán)值、4比特輸出下ResNet-18任務(wù)中的平均能效達到30.34TOPS/W,并可以通過進一步優(yōu)化讀出時序提升到154.04TOPS/W。該工作通過單元、電路及系統(tǒng)面的系統(tǒng)設(shè)計,為高能效、高精度的模擬存內(nèi)計算提供了新思路。

研究成果以“A 28nm RRAM Computing-in-Memory Macro Using Weighted Hybrid 2T1R Cell Array and Reference Subtracting Sense Amplifier for AI Edge Inference”為題發(fā)表在集成電路設(shè)計領(lǐng)域旗艦期刊IEEE Journal of Solid-State Circuits上,微電子所博士研究生葉望為該文章的第一作者、竇春萌研究員為該文章的通訊作者。

(a)基于RRAM的存內(nèi)計算芯片結(jié)構(gòu)框圖,(b)芯片晶圓照片及版圖,

(c)芯片測試數(shù)字波形,(d)芯片參數(shù)

科研工作