近日,微電子所微電子器件與集成技術(shù)重點(diǎn)實(shí)驗(yàn)室劉明院士的科研團(tuán)隊(duì)在HfO2基鐵電存儲(chǔ)器研究領(lǐng)域取得了進(jìn)展,提出了一種基于Hf0.5Z0.5rO2(HZO)材料的鐵電二極管(Fe-diode),并實(shí)現(xiàn)了三維集成。

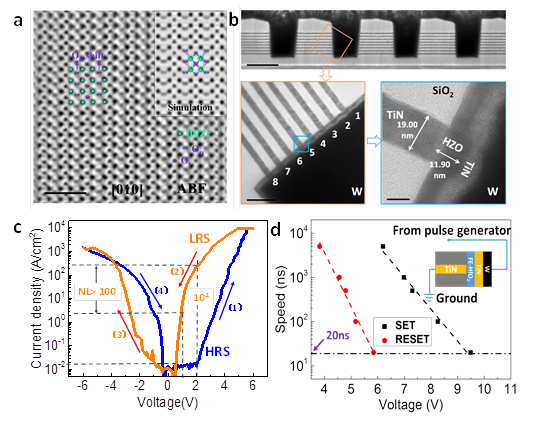

鐵電存儲(chǔ)器具有高速、低功耗、高可靠性的優(yōu)點(diǎn),是下一代非揮發(fā)性存儲(chǔ)器的有力競(jìng)爭(zhēng)者之一。然而,傳統(tǒng)鐵電材料與標(biāo)準(zhǔn)CMOS工藝兼容性差問題和尺寸微縮難的問題制約著鐵電存儲(chǔ)器的發(fā)展。2011年,摻雜HfO2的鐵電材料的問世開啟了鐵電存儲(chǔ)器研究的新時(shí)代。HZO材料的鐵電性起源問題是該領(lǐng)域長(zhǎng)期爭(zhēng)議的焦點(diǎn)。在本項(xiàng)工作中,微電子所科研團(tuán)隊(duì)利用原子分辨率球差校正透射電鏡,觀察到了Hf/Zr和O原子的在晶格中的排列,國(guó)際上首次確認(rèn)了Pca21相的存在,為HfO2鐵電的基礎(chǔ)理論提供了最為直接的證據(jù)。

鐵電存儲(chǔ)器具有高速、低功耗、高可靠性的優(yōu)點(diǎn),是下一代非揮發(fā)性存儲(chǔ)器的有力競(jìng)爭(zhēng)者之一。然而,傳統(tǒng)鐵電材料與標(biāo)準(zhǔn)CMOS工藝兼容性差問題和尺寸微縮難的問題制約著鐵電存儲(chǔ)器的發(fā)展。2011年,摻雜HfO2的鐵電材料的問世開啟了鐵電存儲(chǔ)器研究的新時(shí)代。HZO材料的鐵電性起源問題是該領(lǐng)域長(zhǎng)期爭(zhēng)議的焦點(diǎn)。在本項(xiàng)工作中,微電子所科研團(tuán)隊(duì)利用原子分辨率球差校正透射電鏡,觀察到了Hf/Zr和O原子的在晶格中的排列,國(guó)際上首次確認(rèn)了Pca21相的存在,為HfO2鐵電的基礎(chǔ)理論提供了最為直接的證據(jù)。

不同結(jié)構(gòu)的HfO2基鐵電存儲(chǔ)器(1T1C、FeFET和FTJ)已相繼問世。1T1C結(jié)構(gòu)的鐵電存儲(chǔ)器是破環(huán)性讀取,操作復(fù)雜,對(duì)疲勞特性要求高;FeFET可實(shí)現(xiàn)三維集成,但不能實(shí)現(xiàn)隨機(jī)訪問;FTJ是一種電阻型存儲(chǔ)器,但由于線性低阻態(tài),用于垂直結(jié)構(gòu)的三維交叉陣列中存在串?dāng)_問題。微電子所科研團(tuán)隊(duì)提出了一種新型的HZO基鐵電二極管(Fe-diode)器件,通過極化方向的改變來(lái)控制鐵電二極管導(dǎo)通方向。由于界面勢(shì)壘的存在,該器件具有高度的非線性(>100),可以克服交叉陣列中的漏電,實(shí)現(xiàn)自選通功能。該器件操作速度<20ns,疲勞特性>109,開態(tài)電流密度>200A/cm2,實(shí)現(xiàn)了垂直尺寸小于20nm的三維集成。

上述成果于2020年3月13日以“A highly CMOS compatible hafnia-based ferroelectric diode”為題發(fā)表在Nature Communications期刊上(DOI:10.1038/s41467-019-13827-6)。微電子所羅慶副研究員和華師大成巖副教授為該文章第一作者,微電子所劉明院士、呂杭炳研究員為共同通訊作者。上述工作得到了國(guó)家基金委、科技部、中科院等相關(guān)項(xiàng)目的資助。

全文鏈接:https://www.nature.com/articles/s41467-020-15159-2

圖(a)HZO鐵電相的原子排列。(b)三維垂直結(jié)構(gòu)的TEM圖。

(c)鐵電二級(jí)管的典型IV特性曲線。(d)該器件可以實(shí)現(xiàn)20ns的操作速度。

科研工作