近日,微電子所智能感知研發(fā)中心在低功耗智能感知平臺(tái)研發(fā)方面取得了多項(xiàng)突破性進(jìn)展,成功研制了極低功耗處理器芯片。

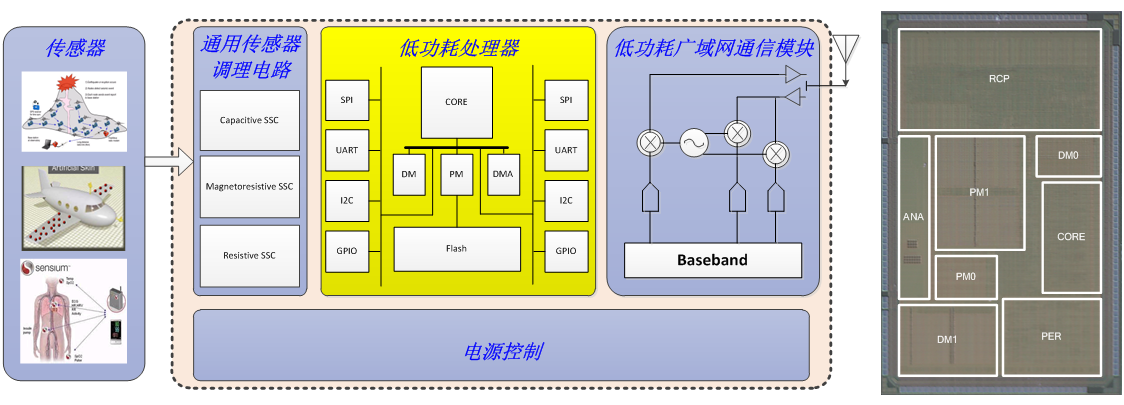

智能感知平臺(tái)(結(jié)構(gòu)如圖1所示)包括通用電阻、電容、磁阻式傳感器調(diào)理電路、低功耗處理器、低功耗廣域網(wǎng)通信模塊,可外掛目前主流的各種傳感器,完成感知層的數(shù)據(jù)分析、特征提取、數(shù)據(jù)壓縮和傳輸層的通信網(wǎng)絡(luò)協(xié)議以及應(yīng)用層的應(yīng)用程序,廣泛應(yīng)用于工業(yè)自動(dòng)化、便攜式設(shè)備、智能家居等領(lǐng)域。低功耗處理器作為智能感知平臺(tái)的核心器件,有著苛刻的功耗要求。

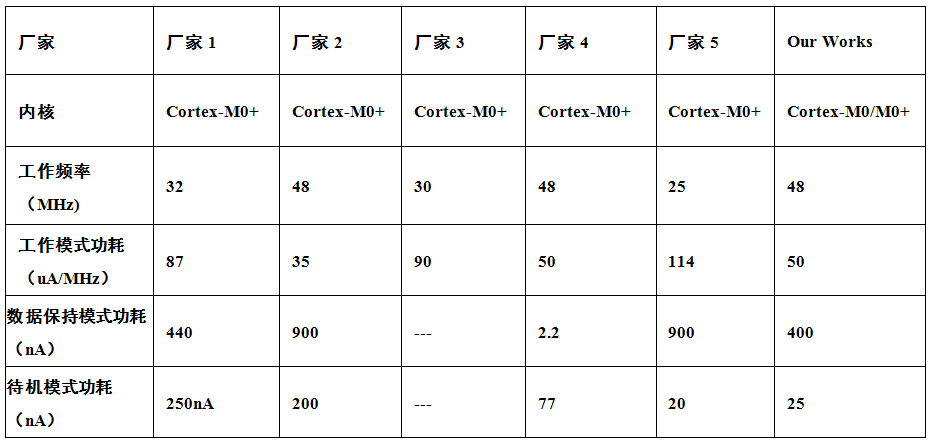

研發(fā)團(tuán)隊(duì)在國(guó)家“863”項(xiàng)目、中科院“先導(dǎo)專項(xiàng)”、國(guó)家自然科學(xué)基金項(xiàng)目的支持下,將近/亞閾值技術(shù)應(yīng)用于此類芯片,同時(shí)綜合采用智能電源/時(shí)鐘管理技術(shù)、超低漏電電路設(shè)計(jì)技術(shù),成功研發(fā)出了極低功耗處理器芯片,功耗指標(biāo)達(dá)到國(guó)際先進(jìn)水平,與同類型芯片的對(duì)比結(jié)果如圖2所示。

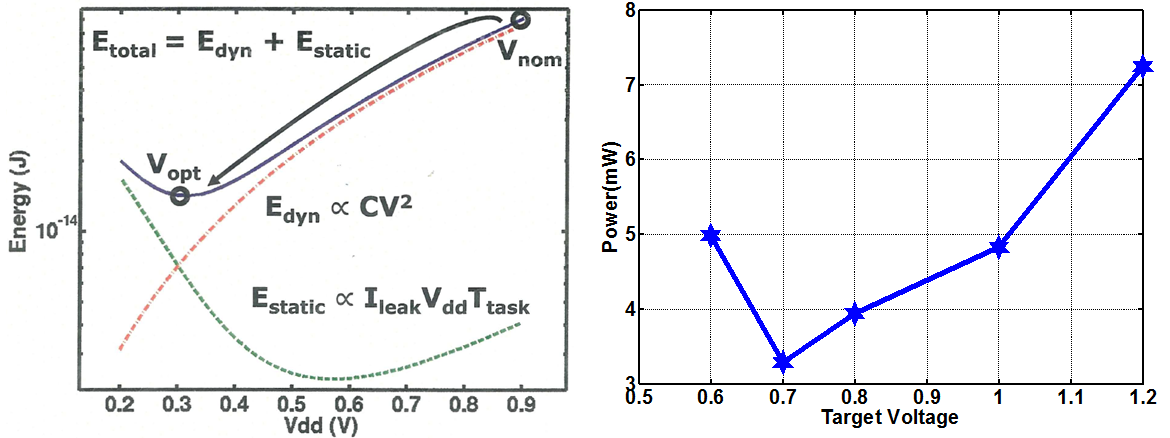

近/亞閾值技術(shù)是近年來(lái)最前沿、最有效的極低功耗技術(shù),能夠同時(shí)優(yōu)化系統(tǒng)的動(dòng)態(tài)功耗及靜態(tài)功耗(如圖3所示)。研發(fā)團(tuán)隊(duì)多年來(lái)一直專注于該技術(shù)的研究,先后研發(fā)出近/亞閾值標(biāo)準(zhǔn)單元庫(kù)、近/亞閾值存儲(chǔ)器、以及支持?jǐn)?shù)字系統(tǒng)的時(shí)序設(shè)計(jì)技術(shù)。通過(guò)綜合采用近閾值晶體管特性、工藝偏差分析、噪聲容限優(yōu)化等前沿技術(shù)手段,這些IP庫(kù)能夠穩(wěn)定工作在0.5V,動(dòng)態(tài)功耗下降19倍,靜態(tài)功耗下降7倍。該芯片采用智能電源/時(shí)鐘管理技術(shù),可支持多種工作模式,包括Active、Low Power Active、Idle、Standby、BackUp、Off等模式,以保證芯片在不同的應(yīng)用場(chǎng)景下,都能夠用最簡(jiǎn)單的邏輯、最低的能量消耗來(lái)完成。為降低待機(jī)模式的漏電功耗,該芯片采用了超低漏電存儲(chǔ)器、超低漏電邏輯設(shè)計(jì)等技術(shù),并結(jié)合精細(xì)的電源及IO管理策略,使得最低模式的漏電功耗僅25nA,達(dá)到當(dāng)前極低功耗處理器芯片的領(lǐng)先水平。

測(cè)試結(jié)果表明,該芯片的性能及功耗指標(biāo)已達(dá)到國(guó)際先進(jìn)水平,滿足工業(yè)計(jì)量、遠(yuǎn)程控制、醫(yī)療電子、無(wú)線傳感等物聯(lián)網(wǎng)節(jié)點(diǎn)的應(yīng)用需求,致力于為快速發(fā)展的物聯(lián)網(wǎng)市場(chǎng)提供業(yè)內(nèi)最低功耗的智能感知平臺(tái)。

圖1 低功耗智能感知平臺(tái)框圖(左)與低功耗處理器芯片(右)

圖2 低功耗處理器性能功耗對(duì)比情況

圖3 低電壓技術(shù)的優(yōu)勢(shì)(左)及本處理器的低電壓效果圖(右)

科研工作